### INVERTER-MACHINE PARAMETRIC CO-DESIGN FOR ENERGY EFFICIENT ELECTRIC DRIVE SYSTEM

By

Jaedon Kwak

Graduate School of Engineering

**Doctoral Thesis**

Department of Mechanical and Electrical System Engineering

KYOTO UNIVERSITY OF ADVANCED SCIENCE

2023

© 2023 Jaedon Kwak

# **Table of Contents**

| Abstr  | act                               |                                                                                                                                                                                                                                                                                                | i                                      |

|--------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Ackn   | owledgn                           | nents                                                                                                                                                                                                                                                                                          | , iii                                  |

| Nome   | enclatur                          | e                                                                                                                                                                                                                                                                                              | V                                      |

| List o | f Symbo                           | ols                                                                                                                                                                                                                                                                                            | .vii                                   |

| List o | f Figure                          | 2S                                                                                                                                                                                                                                                                                             | X                                      |

| List o | f Tables                          | 5                                                                                                                                                                                                                                                                                              | xiv                                    |

| 1      | Introdu                           | iction                                                                                                                                                                                                                                                                                         | 1                                      |

|        | 1.1<br>1.2                        | Background and Motivation1.1.1Sustainable Transportation1.1.2Energy Efficient Electric DriveCo-design of Inverter-Machine1.2.1Interaction between Inverter and Machine1.2.2Necessity of Co-design                                                                                              | 1<br>4<br>7<br>7                       |

|        | 1.3                               | Thesis Outline                                                                                                                                                                                                                                                                                 |                                        |

| 2      | Trends                            | in State-of-the-Art Electric Drives                                                                                                                                                                                                                                                            | .15                                    |

|        | <ul><li>2.1</li><li>2.2</li></ul> | Multi-level Inverter Topology.2.1.1Conventional Two-level Inverter Topology2.1.2Comparison of Multi-level Inverter Topology.2.1.3Three-Level Active Neutral Point Clamped Inverter2.1.4Effect of Multi-level Inverter TopologyWide-band Gap Devices2.2.1WBG Material Properties2.2.2SiC MOSFET | .15<br>.23<br>.28<br>.31<br>.34<br>.36 |

|        | 2.3                               | <ul><li>2.2.3 Comparison Si vs SiC, GaN</li><li>High-Speed, High-Power Density PMSM</li><li>2.3.1 IPMSM</li></ul>                                                                                                                                                                              | .40<br>.42<br>.42                      |

| 2      |                                   |                                                                                                                                                                                                                                                                                                |                                        |

| 3      | Energy                            | Efficient Design Target                                                                                                                                                                                                                                                                        | ,48                                    |

|        | 3.1                               | <ul> <li>Total Energy Consumption During the Drive Cycle</li></ul>                                                                                                                                                                                                                             | .48<br>.50<br>.53                      |

|        | 3.2                               | Overall Power Loss Calculation3.2.1Conduction Loss3.2.2Switching Loss                                                                                                                                                                                                                          | .56                                    |

|   |       | 3.2.3       | Analytical Loss Calculation of 3L-ANPC                |       |

|---|-------|-------------|-------------------------------------------------------|-------|

|   |       | 3.2.4       | Joule Loss                                            | 65    |

|   |       | 3.2.5       | Iron Loss                                             |       |

|   | 3.3   | Summar      | у                                                     | 69    |

| 4 | Com   | puter-aided | l Parametric Inverter-Machine Co-design               | 71    |

|   | 4.1   | -           | d 3L-ANPC Inverter Design with WBG Devices            |       |

|   |       | 4.1.1       | 3L-ANPC Topologies                                    |       |

|   |       | 4.1.2       | PWM Strategies                                        |       |

|   | 4.0   | 4.1.3       | High Switching Frequency                              |       |

|   | 4.2   |             | esign of PMSM                                         |       |

|   |       | 4.2.1       | Increasing Pole Number with High Switching Freq<br>78 |       |

|   |       | 4.2.2       | Inductance Design Considering Co-effect               |       |

|   | 4.3   |             | lation Model                                          |       |

|   |       | 4.3.1       | Inverter Functional Model                             |       |

|   |       | 4.3.2       | FEA Based PMSM Model                                  |       |

|   |       | 4.3.3       | Simulation Results with Co-simulation Model           |       |

|   | 4.4   | Summar      | у                                                     | 91    |

| 5 | Case  | Study-base  | ed Simulation Results                                 | 92    |

|   | 5.1   |             | dy A: 400V B-ISG System for PHEV                      |       |

|   |       | 5.1.1       | Benchmark Design                                      |       |

|   |       | 5.1.2       | Improve Design                                        |       |

|   |       | 5.1.3       | Energy Loss Improvement Results                       |       |

|   | 5.2   |             | dy B: 800V BEV Traction System                        |       |

|   |       | 5.2.1       | Benchmark Design                                      |       |

|   |       | 5.2.2       | Improve Design Using DOE Method                       |       |

|   |       | 5.2.3       | Energy Loss Improvement Results                       |       |

|   | 5.3   | •           | PWM Strategy                                          |       |

|   |       | 5.3.1       | Loss Analysis Based on Load Condition                 |       |

|   |       | 5.3.2       | Comparison of Results                                 |       |

|   | 5.4   | Summar      | у                                                     | 119   |

| 6 | Proof | f-of-concep | t Demonstration                                       | 120   |

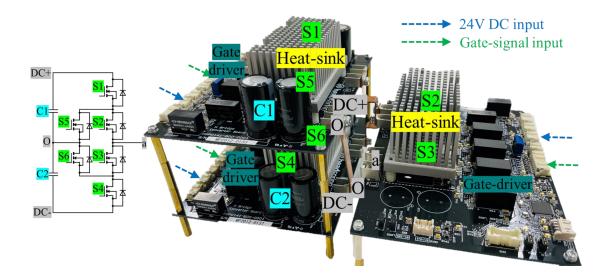

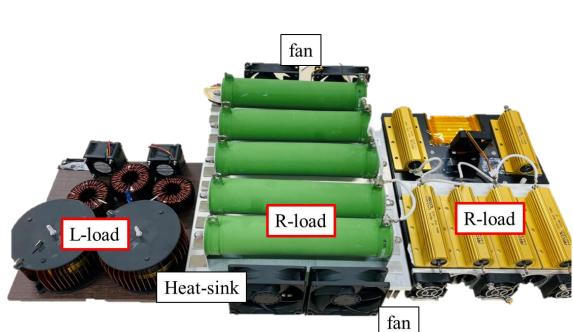

|   | 6.1   | 1           | ental Setup                                           |       |

|   |       | 6.1.1       | Hardware                                              |       |

|   |       | 6.1.2       | Modulation Signals                                    |       |

|   | 6.2   | 1           | ental Results                                         |       |

|   |       | 6.2.1       | Efficiency vs PWM Strategies and Switching Freq 124   | uency |

|   | 6.3   | Summar      | у                                                     | 127   |

| 7 | Conc  | lusions     |                                                       | 128   |

|   |       | 7.1.1       | Summary of Thesis                                     | 128   |

| 7.1.2          | Further Potential Studies |  |

|----------------|---------------------------|--|

| Reference List |                           |  |

### Abstract

This research paper presents an integrated design methodology for the inverter and motor that drive electric vehicles (EVs). As the demand for EVs increases, so does the necessity for research into developing energy-efficient electric drives comprised of inverters and motors. Advances in battery technology are pushing the industry towards the development of high-voltage EV systems, such as 800V systems, which require improvements in rapid charging technology, power density, and energy efficiency. This evolving landscape has sparked increased interest in Wide Band Gap (WBG) devices, particularly Silicon Carbide (SiC) Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFETs) as a replacement for traditional Silicon (Si) Insulated-Gate Bipolar Transistors (IGBTs). SiC-MOSFETs, with their low switching loss, high voltage ratings, and stability at high temperatures, enable high-speed switching, a feature difficult to achieve with Si-IGBTs due to thermal limitations. The paper proposes a comprehensive design strategy that leverages the advantages of these cutting-edge technologies, ultimately contributing to the advancement of efficient and high-performing electric drive systems for future EVs.

However, the move towards high-speed switching also introduces potential issues such as high dv/dt, which can be mitigated by employing techniques like multi-level topology. Among various multi-level topologies, the 3-level Active Neutral Point Clamped (3L-ANPC) topology is receiving substantial attention due to its high reliability and relatively stable loss distribution. While high voltage solutions increase the voltage applied to power devices, multi-level topologies like 3L-ANPC can address this problem by distributing voltage levels. Another benefit of the 3L-ANPC is its capability to implement various Pulse Width Modulation (PWM) strategies. The paper delves into multiple PWM strategies, emphasizing those aimed at energy loss optimization.

Interior Permanent Magnet Synchronous Motors (IPMSMs) are being extensively used in machines, offering advantages like high speed, power density, and stability. Since motors and inverters operate in a mutually influencing manner, it is vital to incorporate this interplay into the design considerations. The research presents a co-simulation model that takes into account the design parameters of both the motor and inverter to analyze systemwide energy loss. The ultimate goal is to use these representative operating points, calculated from several standardized drive cycles, in order to design an electric drive that minimizes energy loss.

## Acknowledgments

First and foremost, I would like to express my deepest gratitude to my supervisor, Dr. Alberto Castellazzi, for his invaluable guidance, support, and encouragement throughout this research journey. His expertise, patience, and insightful feedback were instrumental in shaping this work, and I am truly thankful for the opportunity to learn and grow under their mentorship.

I am also extremely grateful to the members of my thesis committee, Prof. Hiroki Fukushima, Prof. Tadayuki Imai, Prof. Ian Piumarta, and Prof. Taketsune Nakamura for their constructive comments and suggestions that significantly contributed to the refinement of this thesis. Their extensive knowledge and perspectives enriched my understanding of the subject matter and inspired me to think critically and creatively.

I would like to extend my appreciation to my fellow researchers and colleagues, Dr. Hamzeh Jaber, Nagapala Lucky, Sakuraba Yuutarou, and Dr. Tripathi Ravi, for their collaboration, stimulating discussions, and continuous support. I would especially like to thank Lee Yonghwa, who worked closely with me, suggested directions and offered assistance in every possible way. Sharing ideas and tackling challenges together made this journey not only rewarding but also enjoyable.

Additionally, I would like to thank my friends, Vijendran Mugilgeethan, Walid bin Ali, Palani Thiviyathinesvaran, Oscar, Singhaneka Suraj, Srivastava Jagriti, Kshetri Rahul, Dr. Uemura Naoki, and many other colleagues with whom I spent a considerable amount of time during my doctoral studies, for their intellectual discussions and unwavering support. Their camaraderie and encouragement were invaluable to me during this period and helped me to maintain a positive outlook and stay motivated.

Special thanks go to my friends and family, especially my parents, for their unwavering belief in me and their constant encouragement. Their love, support, and sacrifices have been my source of strength and motivation throughout my academic journey. I would also like to express my gratitude to my dear friend Dina, who provided immense support and strength while I pursued my doctorate in a foreign country. Her understanding, and encouragement were a source of comfort and resilience during the challenging times I faced away from home. Lastly, I would like to acknowledge the financial support received from LG Magna e-powertrain, which greatly facilitated the conduct of this research.

## Nomenclature

- AC Alternating Current

- ANPC Active Neutral Point Clamped

- BEV Battery Electric Vehicle

- BFoM Baliga's Figure of Merit

- CCD Central Composite Design

- CHB Cascade H-Bridge

- DC Direct Current

- DOE Design Of Experiment

- EMF Electro Motive Force

- EV Electric Vehicle

- FC Flying Capacitor

- FEA Finite Element Analysis

- FFT Fast Fourier Transformation

- GaN Gallium Nitride

- HEMT High Electron Mobility Transistors

- IGBT Insulated-Gate Bipolar Transistor

- IPMSM Interior Permanent Magnet Synchronous Motors

- LC-PWM Low Conduction Pulse Width Modulation

- LS-PWM Low Switching Pulse Width Modulation

- LUT Look-Up Table

- MI Modulation Index

- MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

- NEDC New European Drive Cycle

- PF Power Factor

- PHEV Plug-in Hybrid Electric Vehicle

- PMSM Permanent Magnet Synchronous Machine

- PWM Pulse Width Modulation

- RSM Response Surface Method

- SBD Schottky Barrier Diode

- Si-Silicon

- SiC Silicon Carbide

- SPWM Sinusoidal Pulse Width Modulation

- SVPWM Space Vector Pulse Width Modulation

- THD Total Harmonic Distortion

- VSI Voltage Source Inverter

- WBG Wide Band Gap

- WLTP Worldwide Harmonized Light Vehicles Test Procedure

# List of Symbols

- $A_F$  Frontal area of Vehicle

- $B_g$  Air-gap flux density

- $C_{rr}$  Rolling resistance coefficient

- $C_d$  Air-drag resistance coefficient

- $D_r$  Rotor diameter

- $E_{crit}$  Critical electric field

- $E_{cycle}$  Energy loss during driving cycle

- $E_{on}$  Turn-on switching loss

- $E_{off}$  Turn-off switching loss

- $E_g$  Energy band gap

- $\varepsilon_r$  Dielectric constant

- $f_s$  Switching frequency

- $F_a$  Aerodynamic drag force

- $F_c$  Climbing gradient force

- $F_{drive}$  Driving force

- $F_m$  Acceleration force

- $F_r$  Rolling resistance force

- g Air-gap length

- $i_a$  Phase current

- $i_d$  d-axis current

- $i_q$  q-axis current

- $i_C$  Collector current

- $i_D$  Drain current

- $k_c$  Carter's coefficient

- L Inductance

- $L_d$  d-axis inductance

- $L_q$  q-axis inductance

- $l_{stk}$  Stack length

- $m_a$  Modulation index

- $m_f$  Frequency modulation index

- $M_v$  Vehicle mass

- n Doping density

- $n_i$  Intrinsic carrier concentration

- $n_p$  Number of poles

- $n_T$  Number of series turns per phase

- $P_{cond}$  Conduction loss

- $P_{CU}$  Joule loss (Copper loss)

- $P_{ED}$  Electric drive loss

- $P_{mag}$  Magnet eddy current loss

- $P_{iron}$  Iron loss

- $P_{sw}$  Switching loss

- q Electric charge

- $R_a$  Phase resistance

- $r_{on}$  On-state resistance

- $R_{CE}$  Collector-emitter resistance

- $R_{DS}$  Drain-source resistance

- $R_F$  Forward resistance

T - Torque

- $T_m$  Magnetic torque

- $T_r$  Reluctance torque

- $T_j$  Junction temperature

- TDR Tire dynamic radius

- $V_{BD}$  Breakdown voltage

- $V_{DC}$  DC-link voltage

- $v_d$  d-axis voltage

- $V_{LL}$  Line-to-line voltage

- $v_{sat}$  Saturation velocity

- $v_q$  q-axis voltage

- $W_{drift}$  Drift region thickness

- $\beta$  Current phase angle

- $\rho$  Air density

- $\mu_0$  Vacuum permeability

- $\mu_n$  Electron mobility

- $\omega_e$  Electrical rotational speed

- $\omega_m$  Mechanical rotational speed

- $\Psi_m$  Magnet flux

- $\varphi$  Power factor

# List of Figures

| Figure | 1.1. Global zero-emission vehicle mandate and internal combustion engine ban, from [3]2                                                                                    |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 1.2. EV stock by different mode, 2022-2030, from [3]                                                                                                                       |

| Figure | 1.3. Schematics of (a) EV (b) PHEV and main components                                                                                                                     |

| Figure | 1.4. Nidec E-Axle: traction electric drive system, from [8]5                                                                                                               |

| Figure | a 1.5. Power flow and loss components of (a) inverter (b) motor in electric drive6                                                                                         |

| Figure | 1.6. Iron loss analysis of the machine considering inverter PWM switching frequency                                                                                        |

| Figure | a 1.7. Current ripple depending on (a) $V$ and $L$ ; (b) $f_s$                                                                                                             |

| Figure | 1.8. Heat damage during high-temperature operating durability test due to excessive magnet eddy current loss by unintended current ripple                                  |

| Figure | 1.9. Magnet eddy current loss analysis results depending on inverter switching frequency                                                                                   |

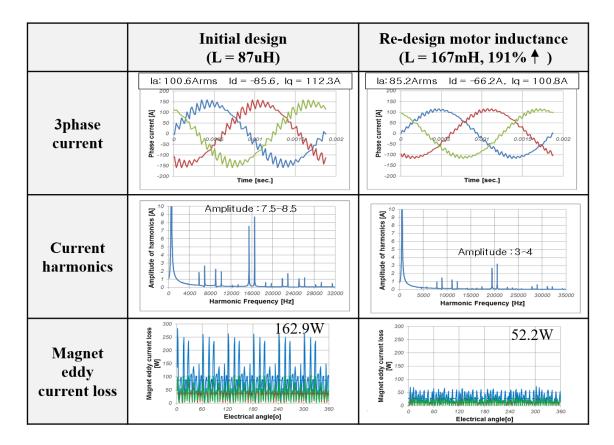

| Figure | 1.10. Magnet eddy current loss analysis results depending on motor inductance. 12                                                                                          |

| Figure | 2.1. Typical two-level three-phase VSI topology16                                                                                                                          |

| Figure | 2.2. Typical Sinusoidal PWM for a two-level VSI16                                                                                                                          |

| Figure | 2.3. Simulated waveform of the two-level VSI operating at $fm = 100Hz$ , $ma = 0.9$ , $mf = 15$ , and $VDC = 400V$ . Load conditions are $L = 20mH$ , and $R = 20\Omega$ . |

| Figure | 2.4. Space vector diagram of a two-level VSI                                                                                                                               |

|        | 2.5. The reference voltage <i>Vref</i> synthesized by <i>V</i> 1, <i>V</i> 2, and <i>V</i> 0 when <i>Vref</i> is at Sector I                                               |

| Figure | 2.6. Typical seven-segment switching sequence for Vref in Sector I22                                                                                                       |

| Figure | 2.7. Three-level NPC inverter topology                                                                                                                                     |

| Figure | 2.8. Three-level FC inverter topology                                                                                                                                      |

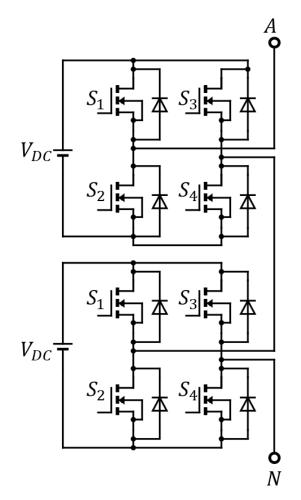

| Figure | 2.9. Five-level CHB inverter topology                                                                                                                                      |

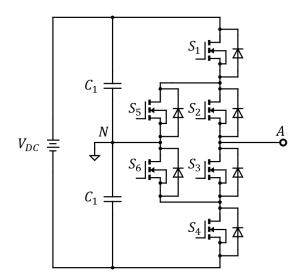

| Figure | 2.10. Three-level ANPC inverter topology27                                                                                                                                 |

| Figure | 2.11. Three-level ANPC inverter topology and current paths (a) P and N state (b) 0 state                                                                                   |

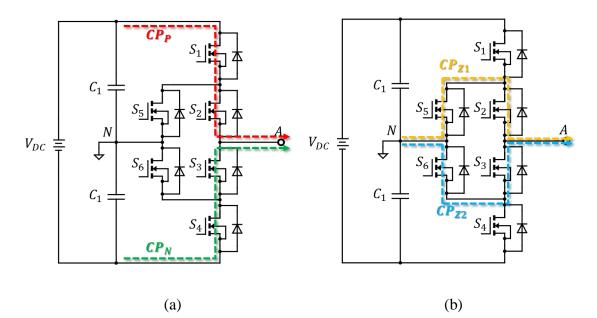

| Figure | 2.12. Different hybrid three-level ANPC topology (a) 4Si-2SiC hybrid1 (b) 4Si-2SiC hybrid2 (c) 2Si-4SiC hybrid                                                             |

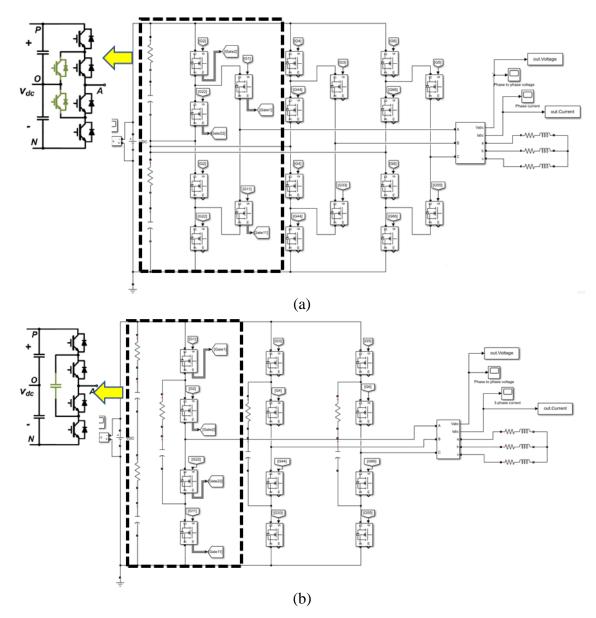

| Figure | 2.13. MATLAB SIMULINK simulation for (a) 3L-ANPC (b) 3L-FC32                                                                                                               |

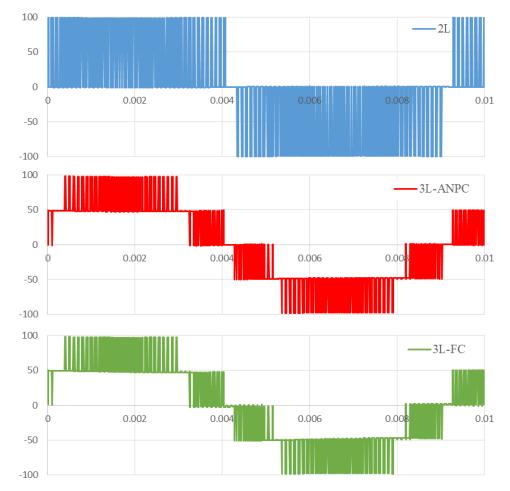

| Figure | 2.14. Comparison of output line-to-line voltage with 2L, 3L-ANPC and 3L-FC33                                                                                               |

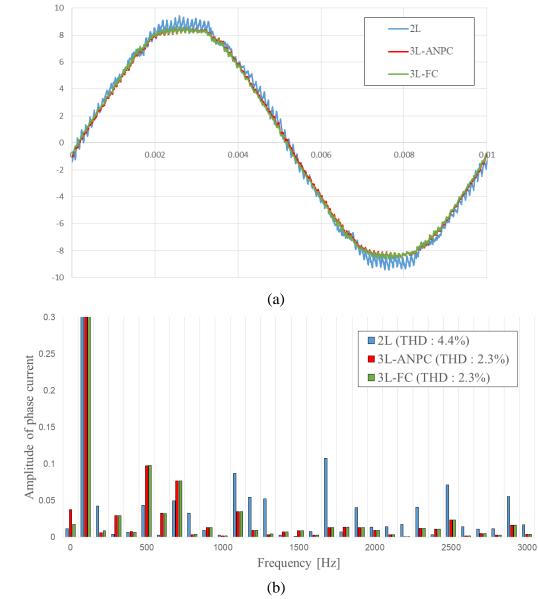

| 0        | 2.15. Comparison of (a) output current (b) harmonics of output current with 2L, 3L-ANPC and 3L-FC                                                                                                   |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

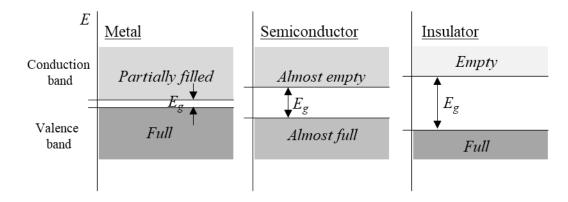

| Figure 2 | 2.16. Energy band diagram of solid metal, semiconductor, and insulator                                                                                                                              |

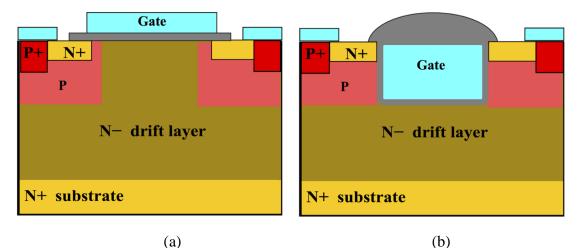

| 0        | 2.17. The structure of (a) Planar SiC-MOSFET (b) Trench SiC-MOSFET, from [60]                                                                                                                       |

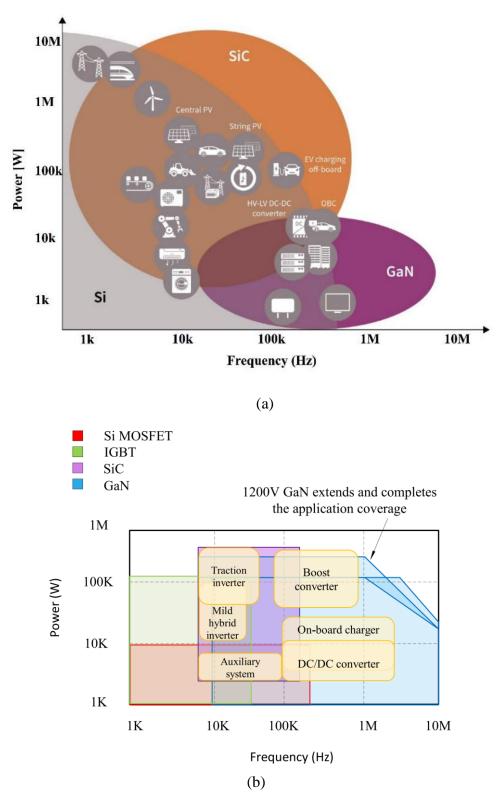

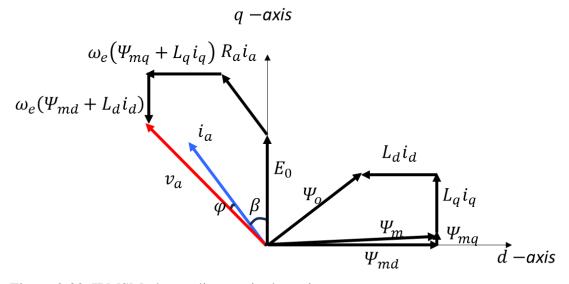

| f        | 2.18. (a) Power-frequency plane of Si, SiC, and GaN for different application,<br>from [60] (b) Power-frequency plane of Si-MOSFET, IGBT, SiC, and GaN for<br>different EVs applications, from [73] |

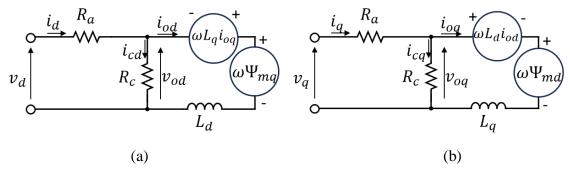

| Figure 2 | 2.19. IPMSM equivalent circuit (a) d-axis (b) q-axis                                                                                                                                                |

| Figure 2 | 2.20. IPMSM phasor diagram in d-q axis                                                                                                                                                              |

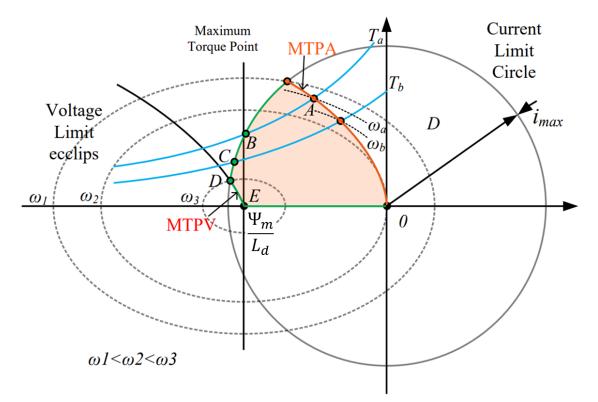

| -        | 2.21. Torque, voltage and current depending on speed characteristics of IPMSM in dq-axis                                                                                                            |

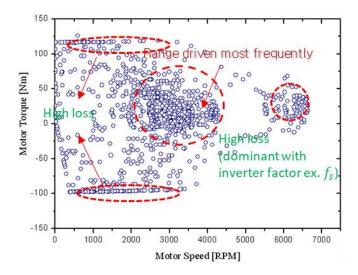

| Figure 3 | 3.1. Example of most frequent operating region of electric drive                                                                                                                                    |

| Figure 3 | 3.2 Example of most frequent operating region of electric drive                                                                                                                                     |

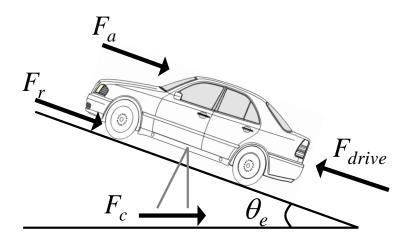

| Figure 3 | 3.3 Longitudinal dynamics of vehicle                                                                                                                                                                |

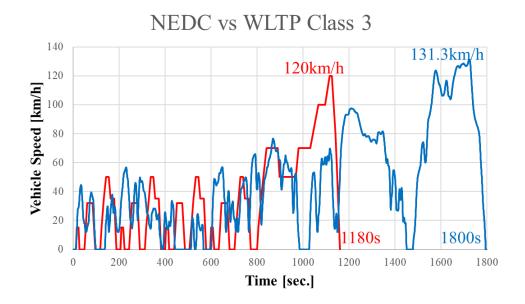

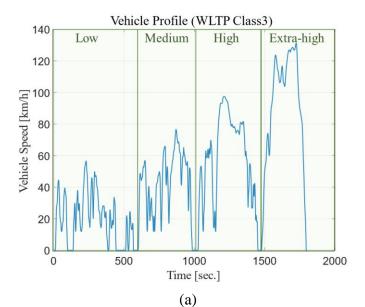

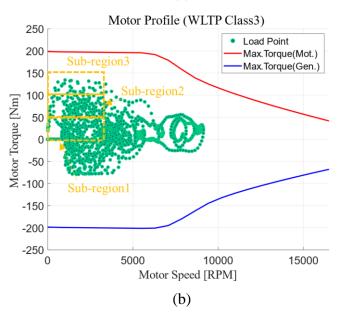

| -        | 8.4. WLTP class 3 drive cycle (a) vehicle profile (time-speed) (b) traction electric drive profile (rotational speed-torque)                                                                        |

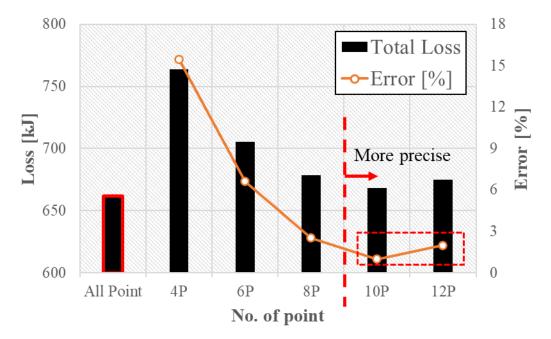

| -        | 3.5 Calculated loss and error between energy gravity center with different no. of point and all drive cycle points                                                                                  |

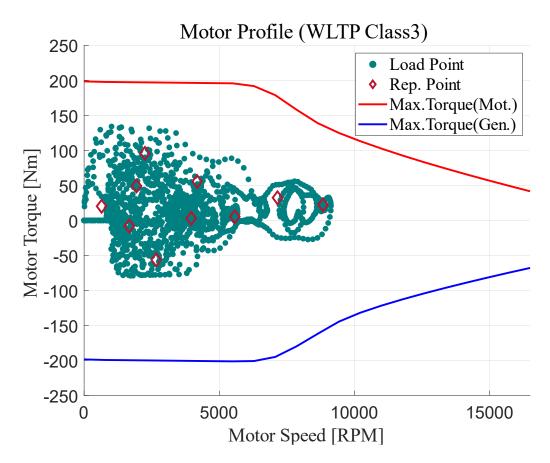

| Figure 3 | 3.6 Ten representative operational points calculated by energy center gravity55                                                                                                                     |

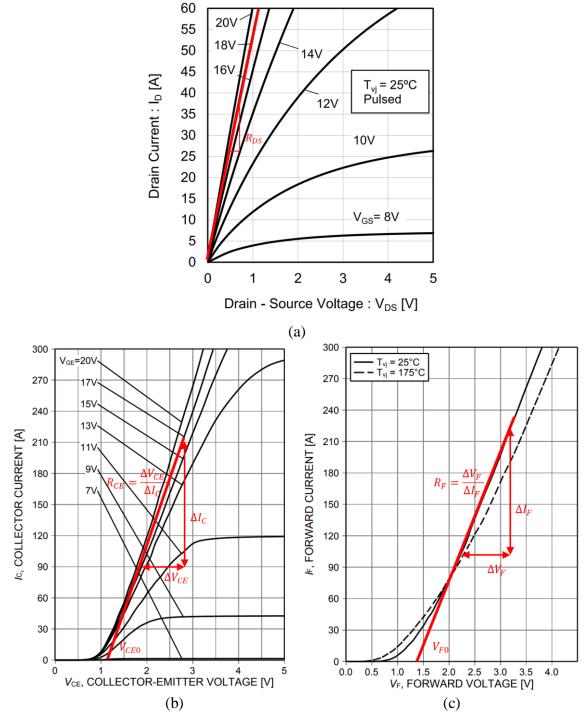

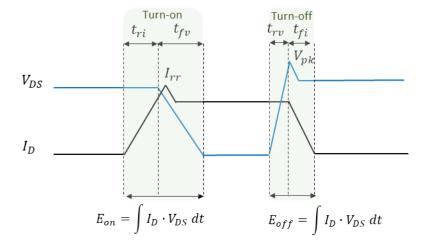

| -        | 8.7 Typical voltage-current characteristics of (a) MOSFETs (b) IGBTs (c) diodes, modified from the datasheet [90,91]                                                                                |

|          | 3.8 Typical waveform of the drain-source voltage and drain current during switch turn-on and turn-off                                                                                               |

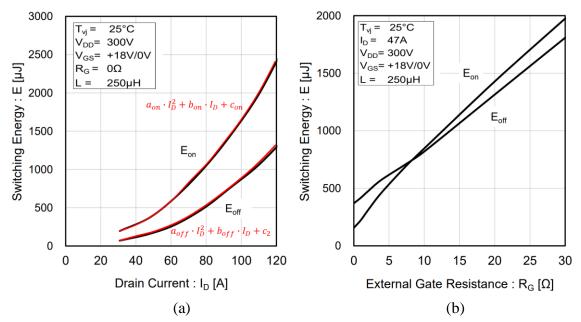

|          | 3.9 Typical switching energy (a) depending on $i_D$ (b) depending on external gate resistance, modified from the datasheet [90,91]                                                                  |

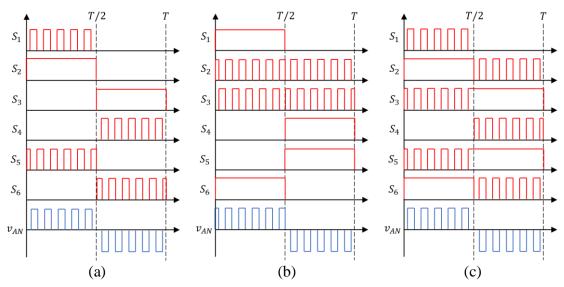

| -        | 8.10 Modulation strategies and corresponding switching sequence (a) PWM1 (b) PWM2 (c) PWM360                                                                                                        |

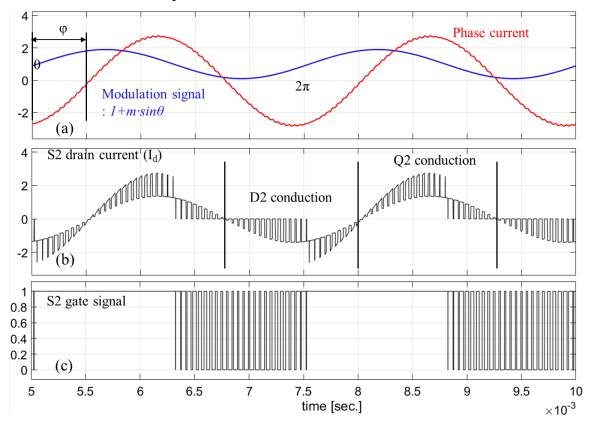

| 0        | 8.11 Conduction and switching loss interval for calculation (a) modulation signal, phase current, and phase angle (b) S2 drain current (c) S2 gate signal                                           |

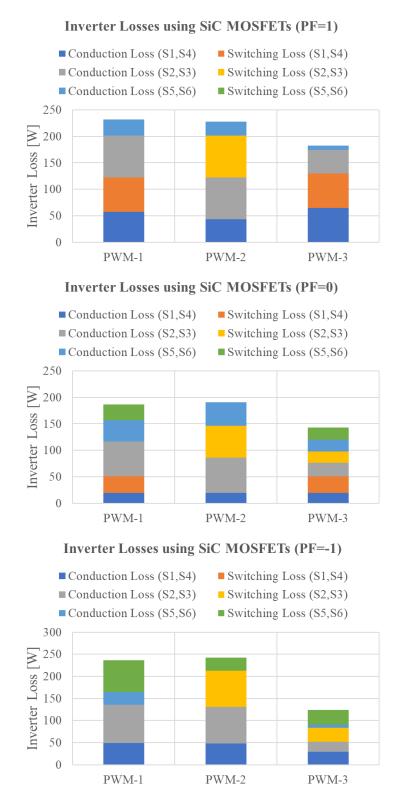

|          | 3.12 Conduction and switching loss calculation results with different PWM strategies (a) $PF = 1$ (b) $PF = 0$ (c) $PF=-1$ 64                                                                       |

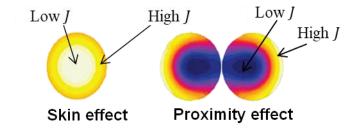

| Figure 3 | 3.13 Concept of the skin effect and proximity effect                                                                                                                                                |

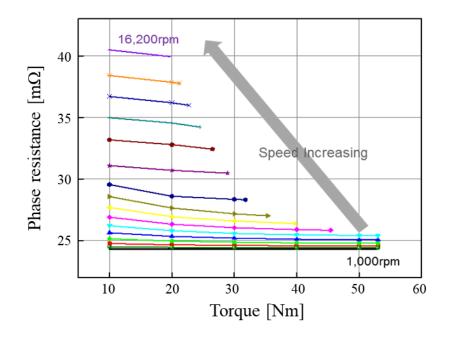

| Figure 3 | 3.14 Phase resistance depending on the load condition; speed and torque                                                                                                                             |

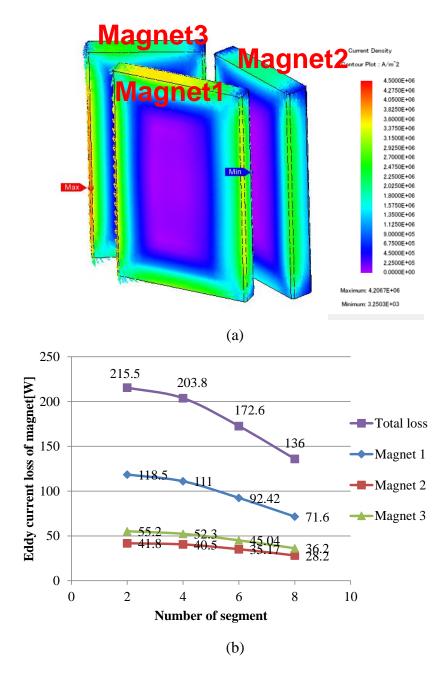

|          | 3.15 (a) Magnet eddy current density in 3D FEA (b) magnet eddy current loss depending on the number of segments                                                                                     |

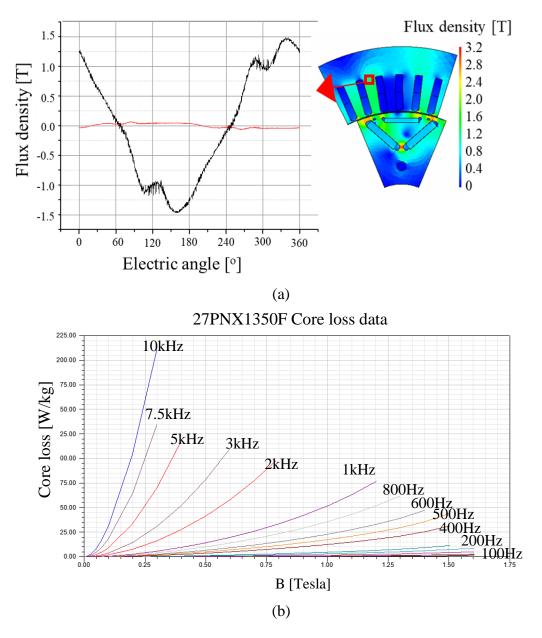

| Figure 3.16 (a) Magnetic flux density analyzed by FEA (b) core loss material data69                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

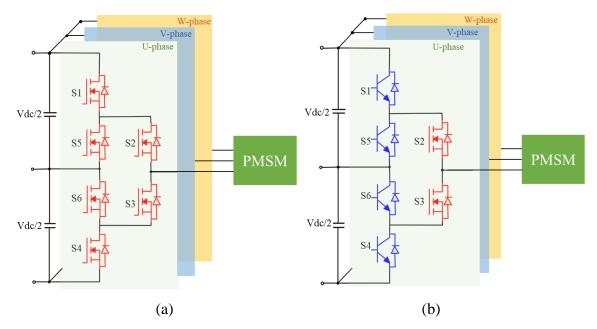

| Figure 4.1. (a) All-SiC 3L-ANPC topology (b) 2SiC-4Si hybrid 3L-ANPC topology72                                                                 |

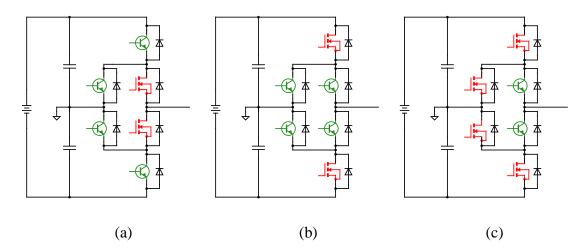

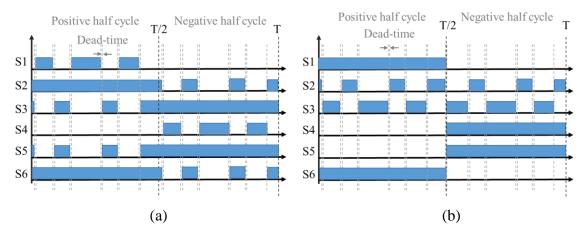

| Figure 4.2. Two different PWM strategies and switching state (a) LC-PWM (b) LS-PWM                                                              |

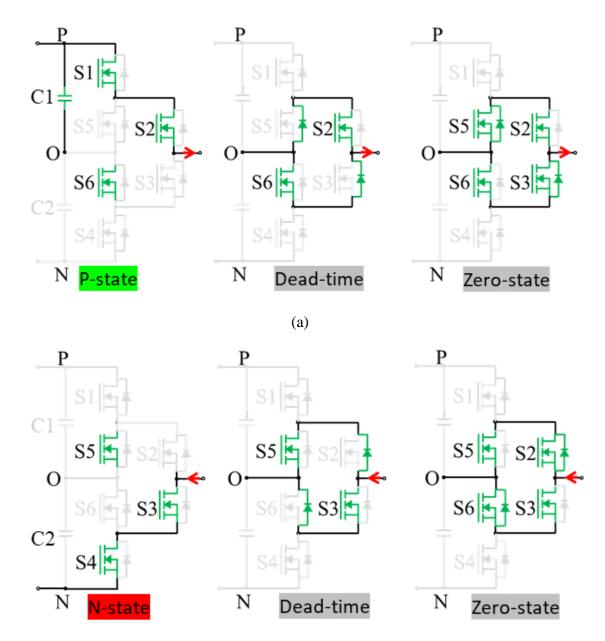

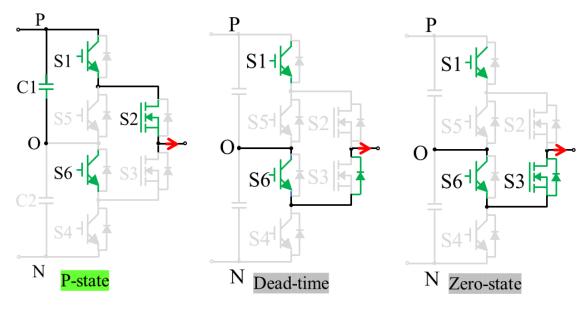

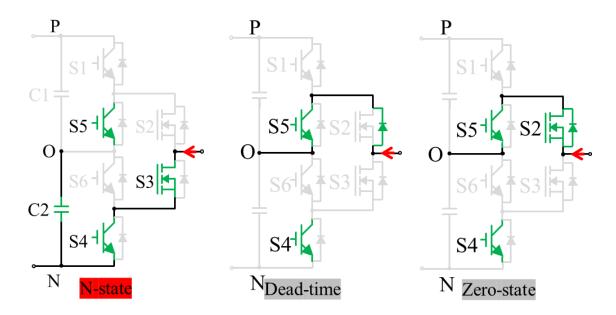

| Figure 4.3. Current path and switch state of LC-PWM at (a) positive half-cycle (b) negative half-cycle                                          |

| Figure 4.4. Current path and switch state at (a) positive half-cycle (b) negative half-cycle                                                    |

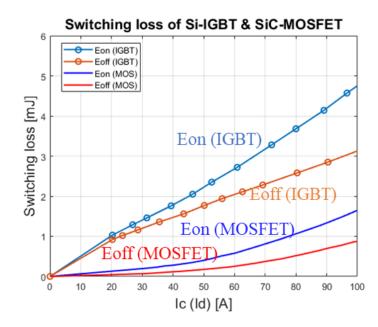

| Figure 4.5 Comparison of switching loss for Si-IGBT/diode and SiC-MOSFET78                                                                      |

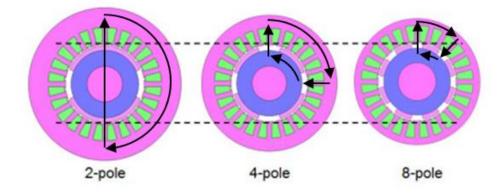

| Figure 4.6 Magnetic flux path and yoke thickness depending on the pole number                                                                   |

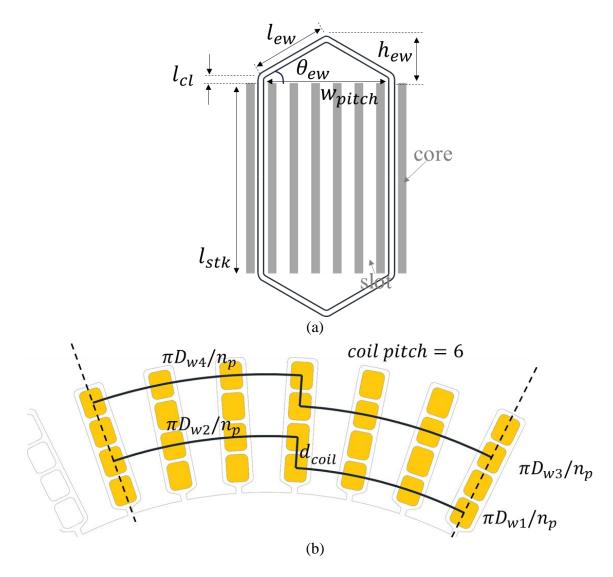

| Figure 4.7 Hair-pin winding geometry (a) side view (b) coil pitch width calculation80                                                           |

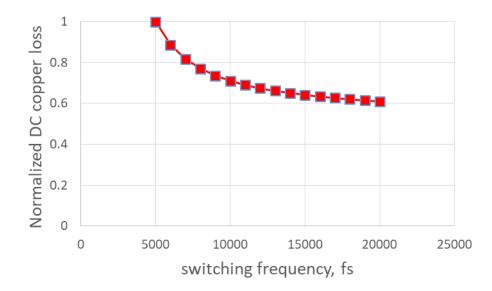

| Figure 4.8 Theoretical calculation of normalized DC copper loss as per switching frequency                                                      |

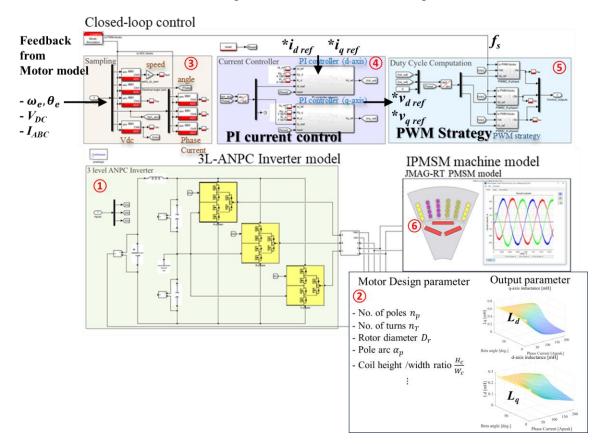

| Figure 4.9 Co-simulation model for evaluating design                                                                                            |

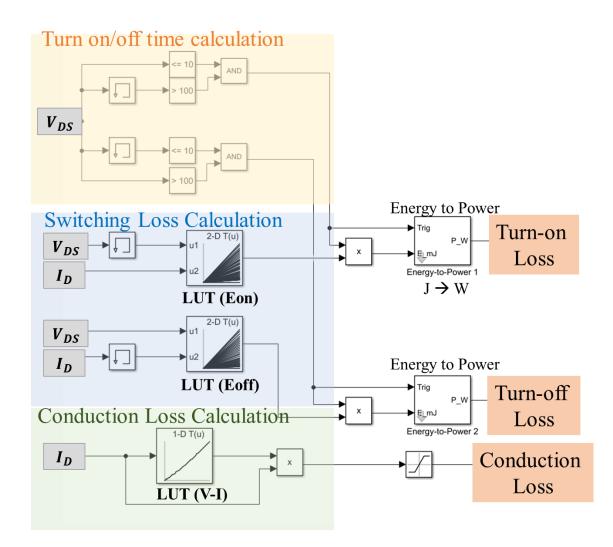

| Figure 4.10 Inverter switching and conduction loss calculation model                                                                            |

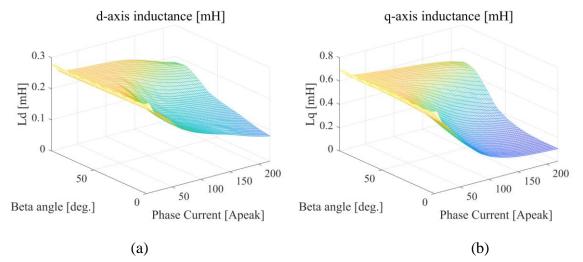

| Figure 4.11 Inductance map of the motor depending on $ia$ and $\beta$ in (a) d-axis $Ld$ (b) q-axis $Lq$                                        |

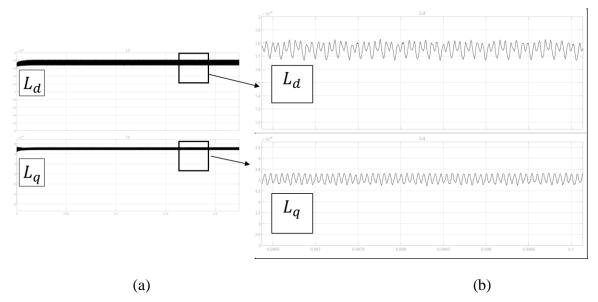

| Figure 4.12 Inductance variation depending on rotor position simulated by using JMAG-<br>RT model                                               |

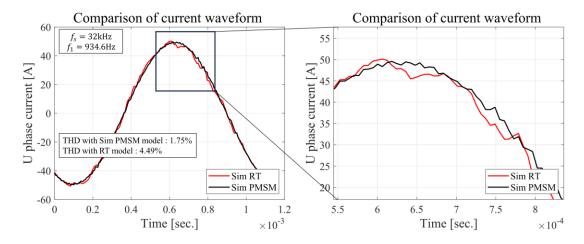

| Figure 4.13 Comparison of the output current waveform (U-phase current) between the simulated by JMAG-RT model and Sim PMSM model               |

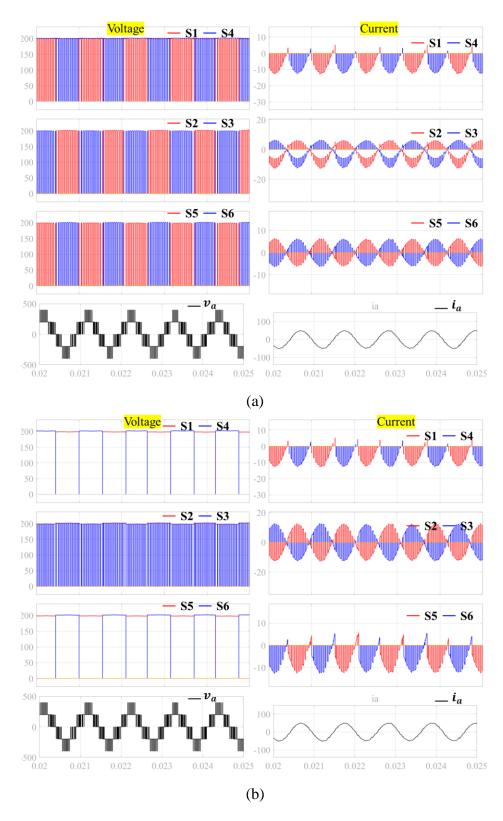

| Figure 4.14 Simulation results: voltage and current for each power device and output load (a) $fs = 20kHz$ , LC-PWM (b) $fs = 20kHz$ , LS-PWM90 |

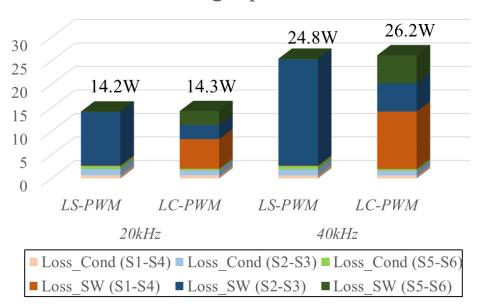

| Figure 4.15 Simulation results: power device loss in single device depending on the PWM strategies and switching frequencies91                  |

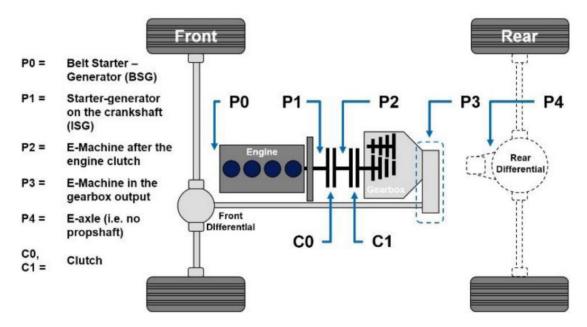

| Figure 5.1 System diagram of the electric machine positions in hybrid electric vehicle,<br>from [106]                                           |

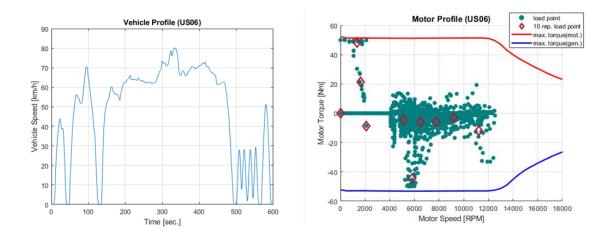

| Figure 5.2 Drive cycle profile (a) vehicle profile (US06) (b) machine profile                                                                   |

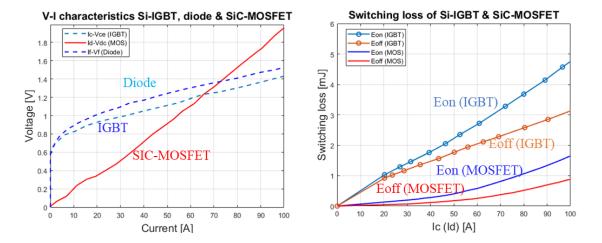

| Figure 5.3 (a) V-I characteristics (b) switching loss of Si-IGBT/diode and SiC-MOSFET for 3L-ANPC                                               |

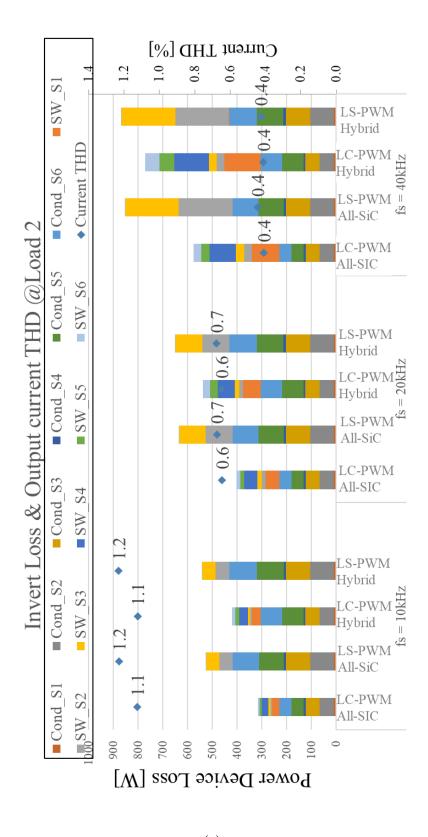

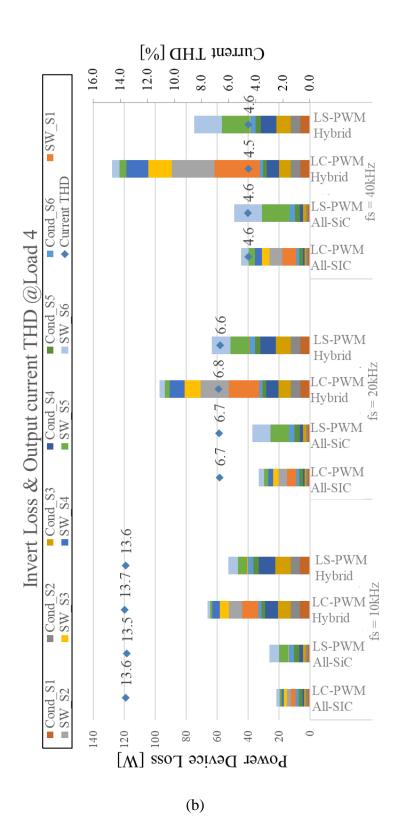

| Figure 5.4 Inverter loss simulation results depending on topologies, PWM strategies, and switching frequencies (a) at Load 2 (b) at Load 4      |

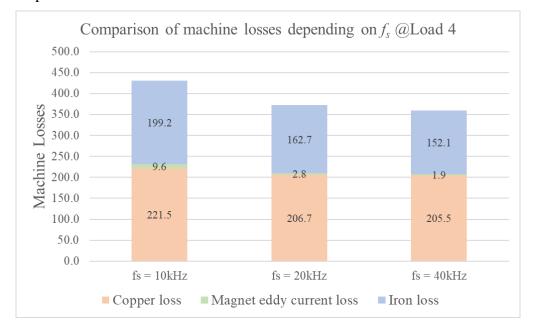

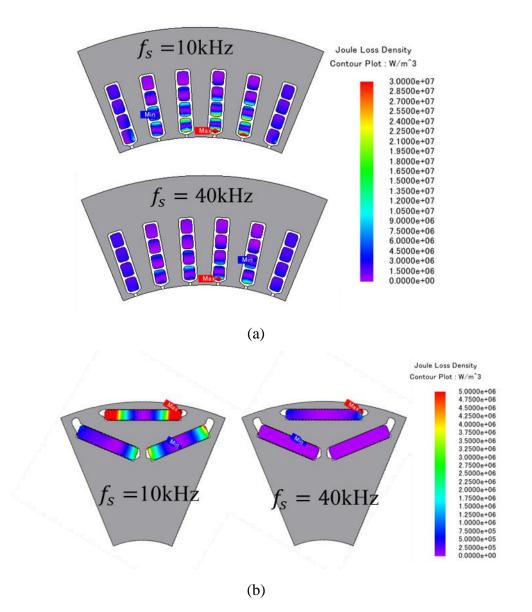

| Figure 5.5 Machine loss simulation based on benchmark design (8pole) depending on switching frequency                                           |

| Figure 5.6 Comparison of loss simulation using JMAG-designer (a) AC Joule loss (b)<br>Magnet eddy loss depending on switching frequency         |

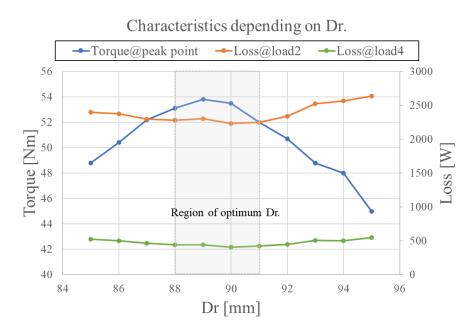

| Figure | 5.7 Peak torque, total loss at load 2, and total loss at load 4 depending on rotor diameter                                                                                                                       |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

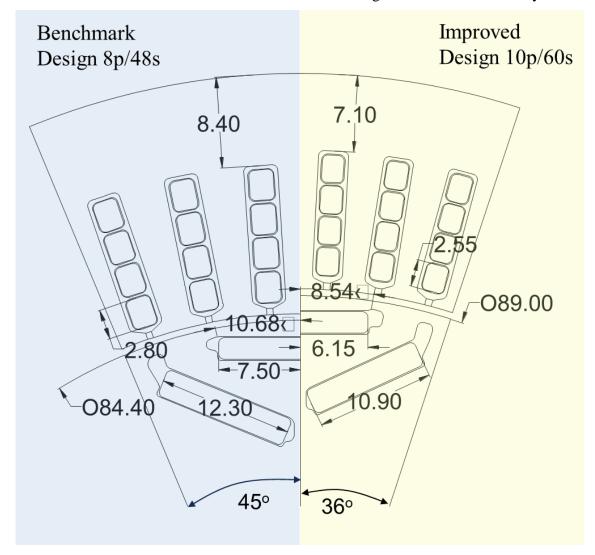

| Figure | 5.8 Comparison of main geometry for the machine design between benchmark and improved                                                                                                                             |

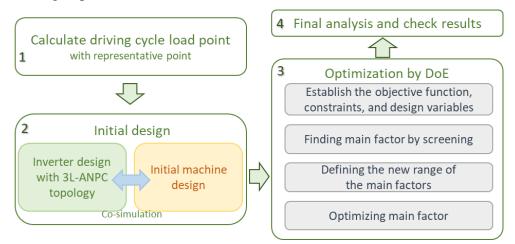

| Figure | 5.9 Design process for energy efficient 800V electric drive with DOE107                                                                                                                                           |

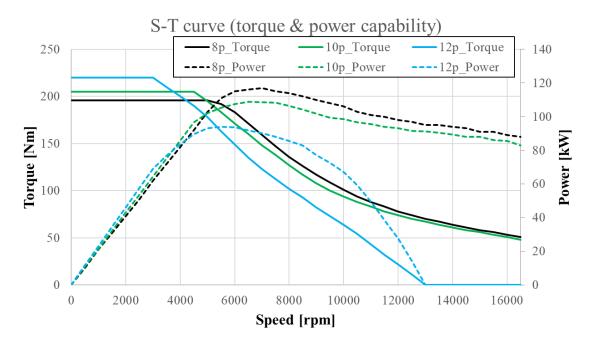

| Figure | 5.10 Speed-torque characteristics of the different pole and slot number with 8/48, 10/60, and 12/72                                                                                                               |

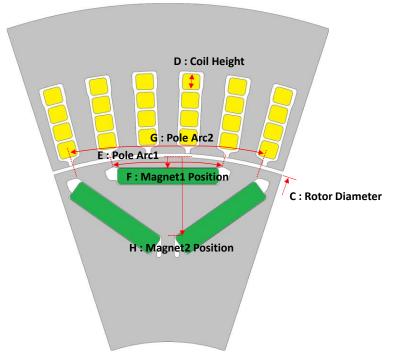

| Figure | 5.11 Initial improved design of machine and design variable for machine geometry                                                                                                                                  |

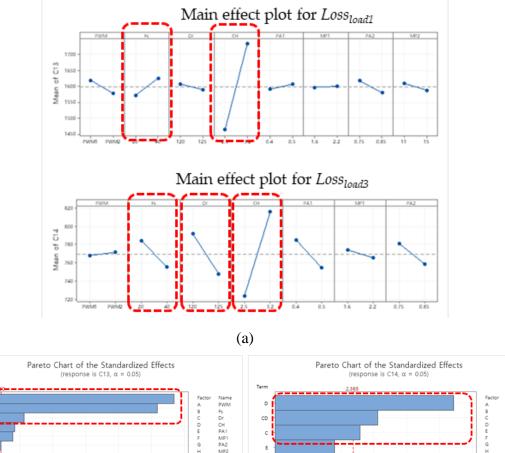

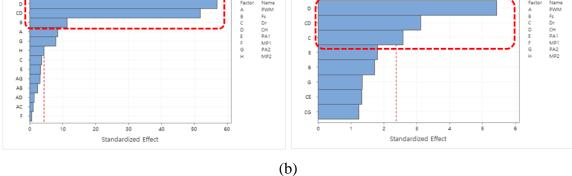

| Figure | 5.12 (a) Main effect plot (b) Pareto chart for finding main factors influencing on loss at load 1 and load 2                                                                                                      |

| Figure | 5.12 Contour plot for loss at load 1 and load 2 vs $CH$ , $D_r$ , and $f_s$ ; min. of $CH$ , max. of $D_r$ and another optimum point of $f_s$ indicates minimizing objective function.112                         |

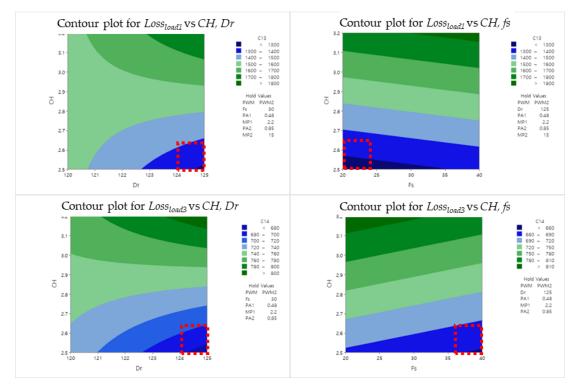

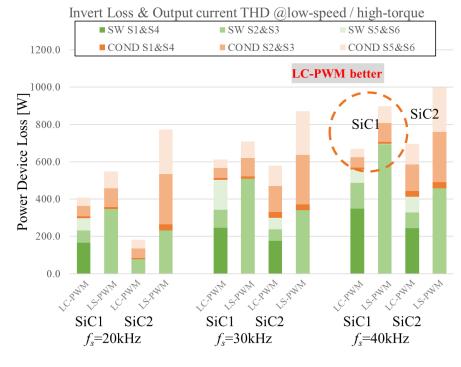

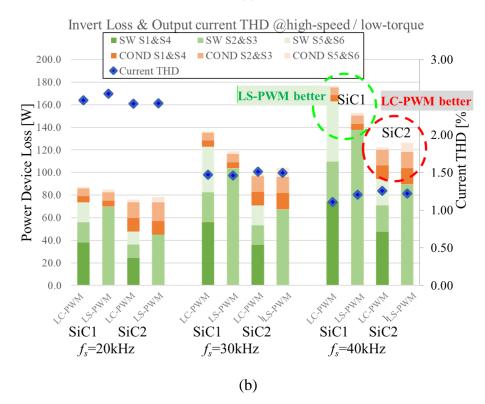

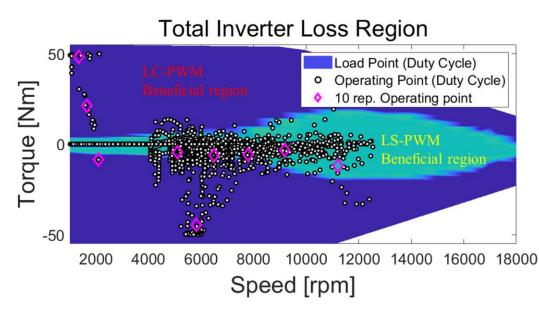

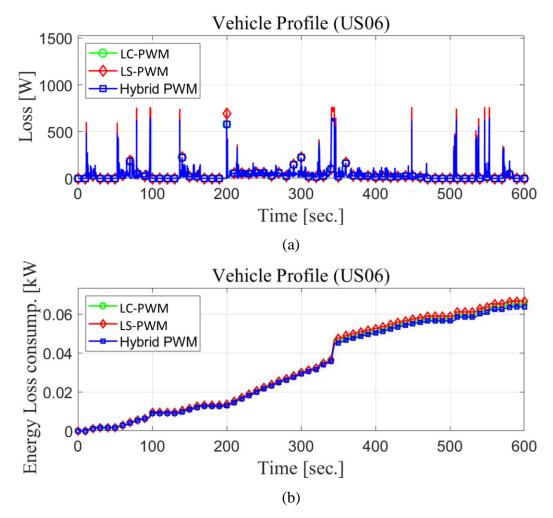

| Figure | <ul> <li>5.14 Inverter losses and output current THD results depending on PWM strategies and switching frequency in representative operating point (a) 1342rpm / 48.3Nm</li> <li>(b) 11,215rpm / 11.9Nm</li></ul> |

| Figure | 5.15 Indication of region where each strategy is advantageous in terms of losses across the entire drive range                                                                                                    |

| Figure | 5.16 (a) Inverter losses during US06 drive cycle in watt. (b) accumulated energy loss consumption in kWh depending on PWM strategy                                                                                |

| Figure | 6.1 Experimental setup with RCP B-Box and 3L-ANPC                                                                                                                                                                 |

| Figure | 6.2 Single phase 3L-ANPC inverter                                                                                                                                                                                 |

| Figure | 6.3 R-L load in parallel and series connection for different load conditions122                                                                                                                                   |

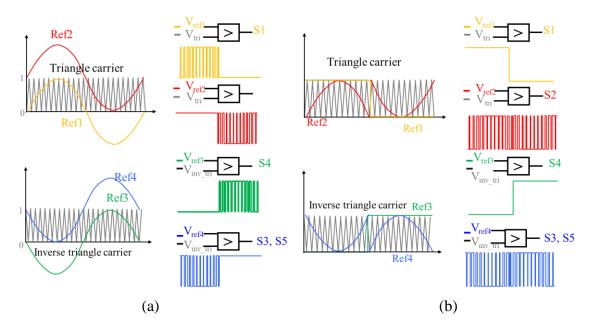

| Figure | 6.4 PWM signal generating by SPWM (a) LC-PWM (b) LS-PWM123                                                                                                                                                        |

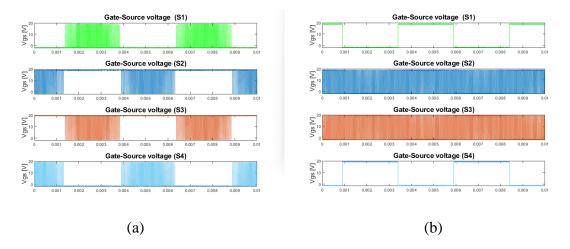

| Figure | 6.5 Experimental PWM signal check generated by RCP B-Box (a) LC-PWM (b) LS-PWM                                                                                                                                    |

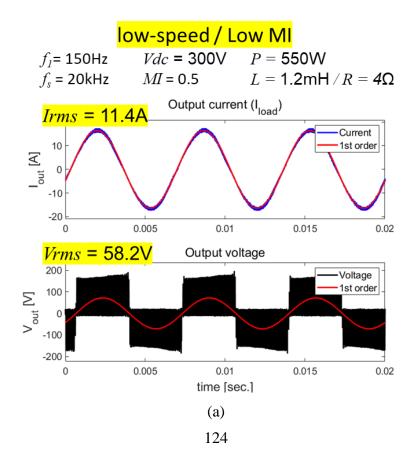

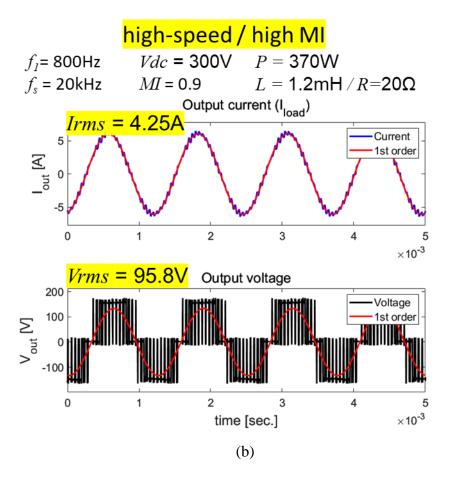

| Figure | 6.6 Output load current and voltage waveform by LC-PWM at (a) load condition 1 (b) load condition 2125                                                                                                            |

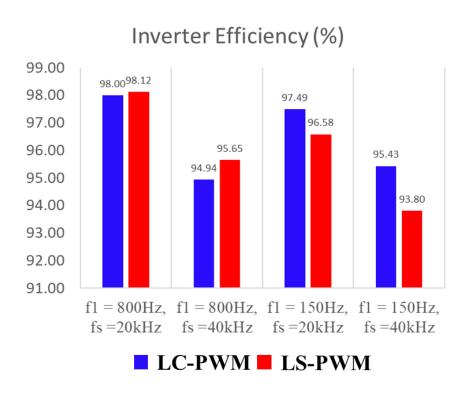

| Figure | 6.7 Efficiency depending on the PWM strategy and switching frequency at two load conditions                                                                                                                       |

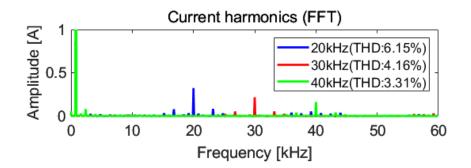

| Figure | 6.8 Current harmonics and THD depending on the switching frequency at 800Hz using LS-PWM                                                                                                                          |

# List of Tables

| Table 2.1. Space vector and on-state switch on 8 switching state of SVPWM                 | 19     |

|-------------------------------------------------------------------------------------------|--------|

| Table 2.2. Comparison of multi-level inverter topologies.                                 | 28     |

| Table 2.3. Switching sequence and output voltage for PWM1 strategy                        |        |

| Table 2.4. Switching sequence and output voltage for PWM2 strategy                        | 30     |

| Table 2.5. Switching sequence and output voltage for PWM3 strategy                        | 30     |

| Table 2.6. Comparison of WBG materials properties with Si, according to [65-              | -67]37 |

| Table 3.1. Comparison of drive cycle (NEDC vs WLTP)                                       | 49     |

| Table 3.2. Vehicle specifications.                                                        | 51     |

| Table 4.1. Switching sequence of LC-PWM strategy                                          | 74     |

| Table 4.2. Switching sequence of LS-PWM strategy                                          | 76     |

| Table 4.3. Simulation conditions                                                          |        |

| Table 5.1. Benchmark 400V B-ISG system specification.                                     | 94     |

| Table 5.2. Representative load point from energy gravity center method                    | 95     |

| Table 5.3. Power device specification for 2L and 3L-ANPC.                                 |        |

| Table 5.4. Two main load point condition.                                                 | 96     |

| Table 5.5. Improved design for $np$ and $nT$ for machine.                                 | 101    |

| Table 5.6. Comparison of inverter and machine loss at each load point                     | 104    |

| Table 5.7. Comparison of energy loss during driving cycle US06                            | 104    |

| Table 5.8. Benchmark specification of 800V traction model                                 | 106    |

| Table 5.9. Design variables, initial value and 2-level variation range                    | 110    |

| Table 5.10.    1/16 fractional factorial design and resutls                               | 110    |

| Table 5.11. Final optimized design value                                                  | 112    |

| Table 5.12. Comparison of energy loss consumption between original benchm improved design |        |

| Table 5.13. Power device specification                                                    | 114    |

| Table 5.14. Energy consumption and improvement by using hybrid PWM on drive cycle.        |        |

| Table 6.1. 3L-ANPC Specification                                                          |        |

| Table 6.2. Load conditions                                                                |        |

|                                                                                           |        |

# **1** Introduction

## 1.1 Background and Motivation

#### 1.1.1 Sustainable Transportation

Efforts towards de-carbonization are ongoing across various industries in pursuit of sustainable development. One of the prominent sectors is the automotive industry, with the accelerated adoption of electric vehicles (EVs) being one of the primary strategies [1]. EVs offer a potent solution to reducing greenhouse gas emissions and achieving sustainable development. Unlike conventional internal combustion engine vehicles, EVs generate zero tailpipe emissions, contributing significantly to improving air quality, particularly in urban environments [2].

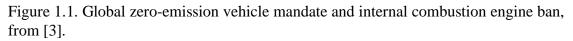

From a policy perspective, governments worldwide are actively promoting the use of EVs [3]. Incentives such as tax rebates, subsidies, and preferential policies, such as access to carpool lanes, are making EVs more attractive to potential buyers. The European Union has implemented new CO2 standards for cars and vans, in alignment with the objectives outlined in the 'Fit for 55' package for 2030. Meanwhile, in the United States, the Inflation Reduction Act (IRA), together with several states adopting California's Advanced Clean Cars II regulation, could drive electric cars to capture a market share of 50% by 2030, in line with the national objective. The introduction of the recently proposed emission standards from the US Environmental Protection Agency is expected to further boost this proportion. Some countries have even announced plans to phase out internal combustion engine vehicles entirely in the coming years. For instance, Norway is aiming for EVs to constitute 100% of its new-car sales by 2025. China's goal is to reach an annual EV sales target of 7 million by 2025, equating to approximately one-fifth of its domestic market demand. France, the United Kingdom, and California in the United States have declared their intentions to cease sales of vehicles powered by internal combustion engines by 2040. Figure 1.1 displays the target timeline for transitioning to zero-emission vehicles in various countries and the ban of internal combustion engine vehicles. Policies in these countries continue to evolve in favor of speeding up the adoption of EVs.

Note: ZEV: Zero emission vehicle, LDV: Light-duty vehicle, HDV: Heavy-duty vehicle

Moreover, the industry level is also demonstrating a commitment toward this transition. Automakers are investing heavily in EV technology and are expanding their EV offerings. Introducing more EV models across various segments creates greater choices for consumers, further boosting EV adoption. Tesla, one of the leading companies, has set a goal of producing 20 million EVs annually. General Motors has made a declaration to halt the sale of gasoline and diesel vehicles by 2035. Similarly, Toyota, a pioneer in hybrid vehicle technology, plans to roll out 70 electrified models by 2025, out of which 15 are expected to be battery electric vehicles (BEVs). Volkswagen, a traditional titan of the internal combustion engine vehicle industry, has stated that 2026 will be its final year to introduce a new internal combustion engine platform [4].

Owing to these policies and the active push for a shift towards EVs by automakers, predictions from the automobile industry suggest an eight-fold or greater increase in the EV fleet by 2030. This describes that the market for EVs is escalating at an average annual rate of approximately 30%. Figure 1.2 illustrates the forecast for the EV market under the declared policy scenarios and the Net Zero Emission 2050 scenario put forward by the International Energy Agency (IEA).

Figure 1.2. EV stock by different mode, 2022-2030, from [3].

**Note:** In order to meet the Net Zero Emissions 2050 target, set forth by the IEA, there is a need for a greater transition to EVs beyond what has been proposed in Stated Policies Scenario. PLDV: Passenger light-duty vehicle, LCV: Light commercial vehicle, PHEV: Plug-in hybrid electric vehicle

#### **1.1.2 Energy Efficient Electric Drive**

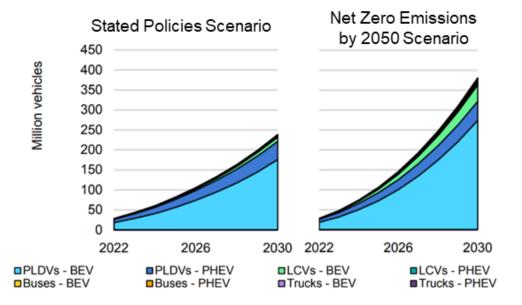

The growing demand for EVs suggests a bright and sustainable future, however, there are still significant challenges to overcome. Some of the most prominent among these include the limited driving range offered by current battery technology and the need for a widespread and reliable charging infrastructure [5]. While improving battery technology is a crucial part of the solution, equal emphasis must also be placed on developing more efficient and powerful traction electric drives that can deliver better performance within the constraints of existing battery capabilities [6,7]. The traction electric drive system plays a pivotal role in determining an EV's performance, energy efficiency, and overall driving range – the key factors contributing to the EVs market success. When a high-power density electric drive is deployed, it allows for a decrease in the system's size and weight while maintaining or even increasing the output power. This attribute is particularly critical in the context of EVs, where both space and weight are of the utmost importance. A lighter and more compact drive system can lead to an increase in the vehicle's energy efficiency, thereby contributing to an enhanced driving range. Equally, high-efficiency design ensures that a large proportion of the electrical energy drawn from the battery is effectively converted into mechanical power for propelling the vehicle, rather than being wasted as heat. Drive systems with high efficiency not only reduce energy consumption but also extend the driving range and overall lifespan of the battery. Within the architecture of an EV, the traction electric drive majorly consists of the inverter and machine. Additionally, it encompasses elements such as gear reducers and, in certain situations, a DC-DC converter. Figure 1.3 provides a schematic representation of the topologies used in EVs and Plug-in Hybrid Electric Vehicles (PHEVs). The electric drive, which is the central focus of this study, is highlighted by the red line in this schematic. In summary, advancements in the design of traction electric drives are fundamental to overcoming the present-day challenges of electric vehicles. By leveraging such developments, strides can be made towards higher energy efficiency, increased driving range, and ultimately, a wider adoption of EVs.

Figure 1.3. Schematics of (a) EV (b) PHEV and main components.

The inverter serves to convert the Direct Current (DC) power from the battery into Alternative Current (AC) power, which in turn drives the motor, ultimately propelling the vehicle. The precise design and operation of these two components are critical to the overall performance, efficiency, and driving range of the vehicle, thereby making them crucial areas of study in the advancement of EV and PHEV technology. Figure 1.4 provides an illustration of a traction electric drive system, which primarily consists of inverter, motor, and reducer [8].

Figure 1.4. Nidec E-Axle: traction electric drive system, from [8].

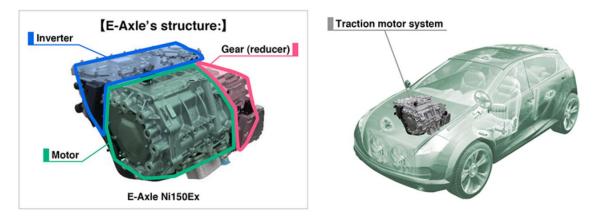

Figure 1.5. Power flow and loss components of (a) inverter (b) motor in electric drive.

Figure 1.5 illustrates the primary energy losses that occur within an electric drive system. The process begins with a high-voltage battery supplying DC electrical input. This energy is then converted into an AC by the inverter to power a three-phase AC motor. During this conversion process, multiple forms of energy losses occur, including conduction losses, switching losses, off-state losses, and gate driver losses. Conduction losses arise due to the current flow within the inverter. Essentially, these are the losses experienced when electricity conducts through the semiconductor devices in the inverter.

Switching losses, on the other hand, are associated with the transition of power switches within the inverter. They occur as power devices switch on/off to generate the desired voltage waveform that drives the motor [9]. Further energy losses can be attributed to parasitic components during off-states and the operation of gate drivers. Off-state losses happen when the power devices in the inverter are not conducting but still lose a small amount of power due to leakage currents [10]. Gate driver losses are incurred when the gate drivers, which control the switching of the power devices in the inverter, operate [11]. The motor operates by receiving three-phase AC power, controlled by the inverter, and transforms it into mechanical power. During this transformation, several forms of energy losses occur. One of these is Joule losses, which encompasses copper losses and magnet eddy losses in the case of a Permanent Magnet (PM) motor. Copper losses is generated from the current flowing through the motor's wire. Additionally, iron loss occurs due to changes in flux within the magnetic core. Furthermore, mechanical loss, originating from the friction generated by the rotation of the motor, impacts energy efficiency. Factors influencing mechanical loss include the rotor size, its cooling method, and connected parts such as bearings. Interestingly, the direction of energy flow reverses when generating power to charge a battery in an electric drive, but the components involved remain the same. In this study, significant energy loss components are focused on analyzing for an energyefficient electric drive design, highlighted in blue in Figure 1.5. These components include conduction losses and switching losses for the inverter, as well as Joule losses and iron losses for the motor. Understanding and minimizing these losses are critical steps in enhancing the overall efficiency of electric drive systems.

## 1.2 Co-design of Inverter-Machine

#### **1.2.1 Interaction between Inverter and Machine**

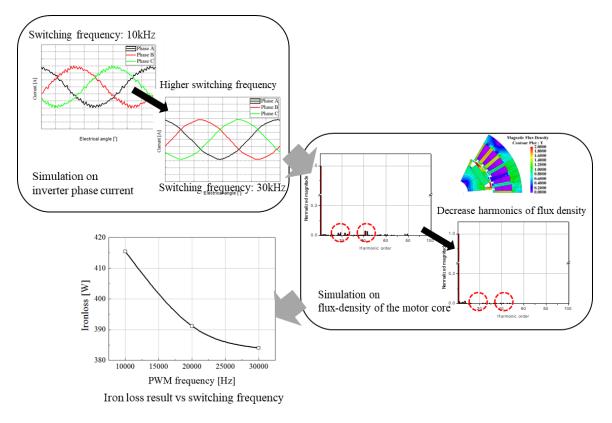

Inverters and machines in electric drives do not operate in isolation; rather, they interact significantly with each other. While the losses of inverters and machines can be calculated separately as discussed in the previous chapter, it is important to consider the influence they exert on each other's parameters. When evaluating and designing a machine, the ideal sinusoidal current could be used to analyze it for the sake of computational efficiency. However, this can result in significant discrepancies in terms of loss prediction, particularly in high-speed regions where frequency impacts are substantial. Machine losses can considerably vary depending on the pulse-width modulation (PWM) control performance determined by the inverter. Therefore, it is essential to estimate motor losses, considering PWM. Figure 1.6 illustrates the current waveform based on the inverter's PWM switching frequency, the change in the machine's flux density, and the results of the iron loss analysis in relation to the switching frequency. As the PWM switching frequency is increased, the high-frequency harmonic component linked to the machine core's flux density change diminishes. As the current waveform becomes closer to the sinusoidal shape due to the increase in PWM switching frequency, this results in a decrease in iron losses. thereby enhancing the overall efficiency of the electric drive system. However, in the inverter, an increased switching frequency leads to greater switching losses in power device. Thus, to maximize the efficiency of the entire electric drive system, it is imperative to design an optimal switching frequency.

Figure 1.6. Iron loss analysis of the machine considering inverter PWM switching frequency.

Moreover, fluctuations in the motor back electromotive force (EMF) exceeding voltage limits, or significant voltage instability due to high harmonic content, can reduce the inverter's control performance. Thus, if the inverter losses are analyzed based on an ideal machine model, the estimation can deviate significantly from the actual scenario. Many studies have been conducted to analyze system losses, compensating for these issues [12-14]. However, research on designing the parameters for inverter and machine from the initial design stage, considering their interaction, is still limited. In industrial contexts, work towards the optimal design of each inverter and machine is actively progressing. Yet, design considerations taking into account the parameters of the inverter and machine and their co-effect are often overlooked. Consequently, this study aims to propose a co-design methodology that considers the interaction between the inverter and machine from the initial design stage and to demonstrate the potential improvements this can bring.

#### 1.2.2 Necessity of Co-design

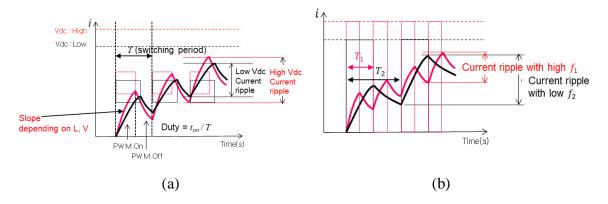

In typical scenarios, the output current of an inverter, serving as the input current of a motor, is sinusoidally modulated to the required frequency and magnitude to drive an AC motor. During the duty ratio D —defined as the on-time  $t_{on}$ , per switching cycle T the current increases, then deflates for the remainder of the time. The adjustment of the duty ratio allows for the formation of the desired current waveform. However, this process invariably gives rise to current ripple. This ripple not only diminishes the efficiency of the motor but also influences vibration and noise performances [15]. Figure 1.7 illustrates the current ripple due to DC-link voltage, switching frequency, and motor inductance. As demonstrated in (a), the larger the input DC voltage of the inverter and the smaller value of the motor inductance, the larger ripple value, as indicated by the red current line. Furthermore, as shown in (b), augmenting the switching frequency—or equivalently, shortening the switching period—can reduce the current ripple under given voltage and inductance conditions. The approximate relationship between the current ripple and each parameter can be expressed through Equation. 1.1, where  $f_s$  represents the switching frequency, V symbolizes the voltage applied to the power device or the input voltage, and L is the motor inductance value.

Figure 1.7. Current ripple depending on (a) V and L; (b)  $f_s$ .

$$i_{ripple} = \frac{1}{L} \int_0^T V dt$$

Equation 1.1

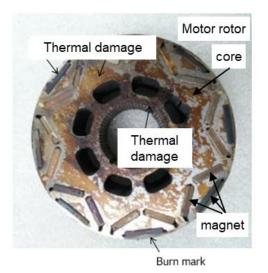

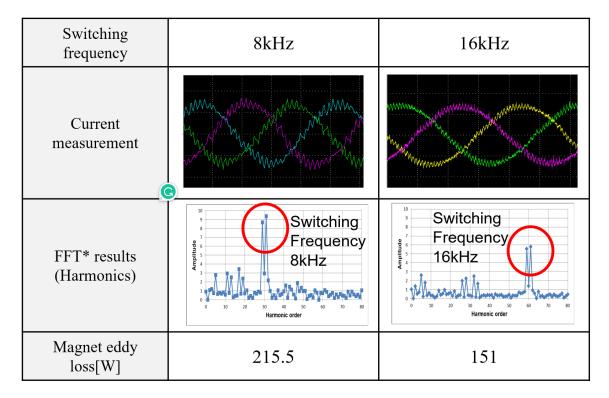

For an energy-efficient electric drive system, it is imperative to minimize the current ripple value, which is substantially influenced by inverter parameters like switching frequency and voltage and the motor parameter inductance. Thus, for optimal system efficiency, a design that reduces current ripple must simultaneously consider these parameters. Figure 1.8 displays the result of an excessive increase in magnet eddy current loss at high speeds due to an unintended current ripple value. This occurs when the design does not sufficiently consider current ripple, resulting in compromised motor performance and damaged reliability due to heat in durability tests. This problem can be resolved by increasing the inverter's switching frequency as displayed in Figure 1.9, which helps reduce the eddy current loss. Additionally, as can be seen in Figure 1.10, this also resolved by redesigning motor for increasing motor inductance. However, a superior outcome can be achieved by proceeding with an optimal design considering both motor and inverter design parameters at the initial design stage. This shows the importance of co-design at the inception of inverter and machine design processes. The implementation of energyefficient electric drive designs can be more economically and efficiently achieved utilizing co-design methodology. Consequently, in this study, a co-design methodology that combines the most recent advancements in the realm of inverters and machines for electric drives is proposed, and the efficacy of these innovations is discussed.

Figure 1.8. Heat damage during high-temperature operating durability test due to excessive magnet eddy current loss by unintended current ripple.

Figure 1.9. Magnet eddy current loss analysis results depending on inverter switching frequency.

**Note:** Using double switching frequency from 8kHz to 16kHz, total magnet eddy current loss is reduced from 215.5W to 151W.

Note: Re-designing motor inductance from  $87\mu$ H to  $167\mu$ H by increasing stator turns, total magnet eddy current loss is reduced from 162.9W to 52.2W.

# **1.3 Thesis Outline**

The full structure of the thesis is as follows.

Chapter 2 delves into the state-of-the-art technology trends related to energyefficient electric drives. Research on inverters using wide-band gap (WBG) devices such as Silicon Carbide (SiC) or Gallium Nitride (GaN), suitable for high-speed applications, is actively being pursued. This chapter explores the unique properties of each WBG material and representative devices, and compares the merits and demerits of traction inverters, particularly from an energy perspective, against conventional silicon (Si) devices. Additionally, various multi-level topologies are discussed, with a specific focus on the topology and modulation techniques of 3-level Active Neutral Point Clamped (3L-ANPC). The chapter concludes with a review of research on high-speed, highly efficient machine technology.

Chapter 3 addresses the methodology and process involved in designing energyefficient electric drive system. Standardized drive cycles and their conversion into electric drive profiles are discussed, with innovative approaches proposed for the selection of representative load points for design considerations. Analytic loss calculations of each inverter and machine losses are included in this chapter.

In chapter 4, the computer-aided parametric co-design methodology is discussed. The detail description of co-simulation model specifically developed for this research is presented. A novel improving design method for designing inverters and machines based on this co-simulation model is introduced. The energy-efficient inverter design utilizing WBG devices and 3L-ANPC topology is proposed, demonstrating that this improved inverter design can yield substantial enhancements in the machine design. With high-speed switching, increasing pole numbers of the machine results in overall boost in system efficiency. Additionally, an improved machine inductance design that takes into account the impact of inverter parameters is discussed, that enables to enhance the efficiency and functionality of the system.

Chapter 5 contains a case study executed using industry-standard models and the methodologies outlined in the previous sections. Simulation results indicate a marked reduction in the total energy consumption over the course of the drive cycle, underscoring the efficacy of the approaches discussed in this study. The case study first delves into the application of a Belt-driven Integrated Starter Generator (B-ISG) in the 400V PHEV system. This is followed by an analysis of the improved design outcomes for an 800V BEV traction system. Finally, based on comparison energy consumption results of the two PWM strategies, a novel idea using hybrid modulation strategy is presented.

In chapter 6, the experimental demonstrations that lend support to the study is focused on. The experimental concept and setup are elaborated upon, with corresponding results for each variable presented. Improved results are generated and showcased through the fabrication and testing of a working prototype. In chapter 7, the results and findings of the research is summarized and the contribution to the field is discussed. Potential avenues for future enhancements and advancements are presented.

# 2 Trends in State-of-the-Art Electric Drives

As discussed in chapter 1, vehicle electrification has been gaining momentum at a swift pace. This rapid progression, experienced over recent years, coincides with a transformative societal shift in transportation, characterized by autonomous mobility and service-driven conveyance, resulting in an expanded sphere of movement. These paradigm shifts instigate the demand for higher power and more efficient electric traction drive systems, thereby enabling enhanced fuel economy for a given battery charge. The U.S. Department of Energy, in conjunction with the U.S. Council for Automotive Research, has crafted a roadmap for electric passenger vehicles projected to 2025 [16]. According to this, a target power density of 33kW/L for a 100kW traction drive, a lifespan of 300,000 miles and 15 years, and a cost of \$6/kW are presented for the development of a passenger car platform for high efficiency, compactness and economy. For the inverter, the objectives are a power density of 100kW/L and a cost of \$2.7/kW, while for the motor, the power density aim strands at 50kW/L and the cost target at \$3.3/kW. These overall aims constitute a daunting objective to curtail costs by 25% and reduce volume by 88% relative to 2020 figures. To fulfill these aims, numerous investigations into inverters and motors have been undertaken [17]. In this chapter, building on a comprehensive literature review, the most recent advancements in efficient electric drive technologies that facilitate the transition to EVs are discussed and elaborated upon.

## 2.1 Multi-level Inverter Topology

#### 2.1.1 Conventional Two-level Inverter Topology

Traction inverters for EVs are dominated by two-level three-phase voltage source inverter (VSI) topology because of its high efficiency, simple control requirements, and low cost [18]. This inverter topology is presented in Figure 2.1. A pair of half-bridges, each made up of two power devices, is linked to each phase of the motor. In this each leg, the top and bottom switches (S1 and S2, S3 and S4, S5 and S6) operates in complementary, and it's critical to ensure they are never switched on simultaneously. Otherwise, a shortcircuit would occur on the input DC link, leading to possible system malfunction or damage. Additionally, the DC-link capacitors (C1, C2) are positioned at the input terminal of the inverter on the side connected to the traction battery. A boost converter can be integrated between the DC input and the inverter. This converter serves to step-up the input DC voltage to the desired level before it is connected to the inverter [19]. This ensures that the voltage delivered to the inverter aligns with its operational specifications, enhancing the overall efficiency and functionality of the system.

Figure 2.11. Typical two-level three-phase VSI topology

Figure 2.12. Typical Sinusoidal PWM for a two-level VSI

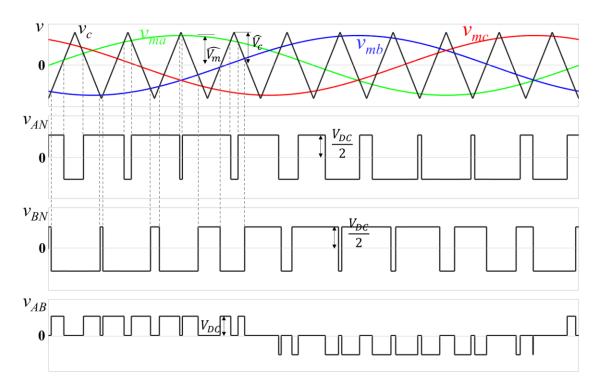

The general operation of a typical Sinusoidal PWM (SPWM) scheme for a twolevel VSI is depicted in Figure 2.2. In this illustration,  $v_{ma}$ ,  $v_{mb}$ , and  $v_{mc}$  represent the threephase sinusoidal modulating waves, and  $v_c$  signifies the carrier wave. The fundamentalfrequency component present in the output voltage of the inverter can be effectively regulated by the amplitude modulation index (MI), as defined in Equation 2.1. The role of the amplitude modulation index here is crucial as it manipulates the fundamental output voltage by adjusting the ratio between the peak amplitude of the modulating waveform,  $\hat{V}_m$ and the peak amplitude of the carrier waveform,  $\hat{V}_c$ . Therefore, through the careful calibration of the amplitude modulation index, the operation and performance of the VSI can be optimized.

$$m_a = \frac{\widehat{V_m}}{\widehat{V_c}}$$

Equation 2.2

The frequency modulation index is defined as represented by Equation 2.2, where  $f_m$  and  $f_c$  refer to the frequencies of the modulating and carrier waves. A higher number of  $m_f$ , which corresponds to a higher carrier frequency, results in enhanced control performance. This is due to the output wave being more closely aligned with the desired waveform.

$$m_f = \frac{f_c}{f_m}$$

Equation 2.3

When the modulating signal exceeds the carrier signal, the switch S1, which is top switch of the A-phase leg is turn-on, and consequently, the bottom switch S2 is turn-off. As a result of this,  $v_{AN}$ , the phase-to-neutral voltage, becomes equivalent to  $+V_{DC}/2$ , where  $V_{DC}$  denotes the DC-link voltage. Conversely, if the carrier signal exceeds the modulating signal, S1 is turn-off while the S2 is turn-on. Consequently,  $v_{AN}$  transitions to  $-V_{DC}/2$ . Sice the waveform of  $v_{AN}$  has only two levels,  $+V_{DC}/2$  and  $-V_{DC}/2$ , the inverter is known as a two-level inverter. A similar control mechanism is also employed for the other phases, ensuring smooth and efficient operation of the inverter. The line-to-line voltage vAB is determined by Equation 2.3.

$$v_{AB} = v_{AN} - v_{BN}$$

Equation 2.4

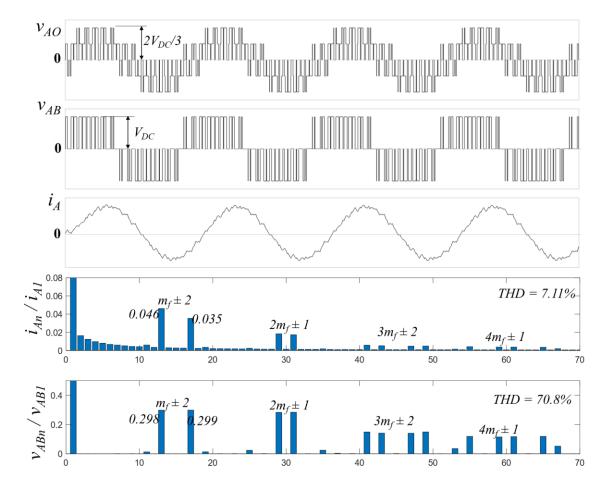

Figure 2.3 presents a set of simulated waveforms for the two-level VSI, where  $v_{AO}$  is the load phase voltage,  $v_{AB}$  is the line-to-line voltage, and  $i_A$  is the load current. The

simulation conditions are  $f_m = 100$ Hz,  $m_f = 15$ ,  $m_a = 0.9$ ,  $v_{DC} = 400$ V, and loads are comprised by three-phase resistance-inductor (R-L), where L=20mH,  $R=20\Omega$ .

Figure 2.13. Simulated waveform of the two-level VSI operating at  $f_m = 100Hz$ ,  $m_a = 0.9$ ,  $m_f = 15$ , and  $V_{DC} = 400V$ . Load conditions are L = 20mH, and  $R = 20\Omega$ .

Due to the process of switching, both voltage and current wave have harmonic components, as demonstrated in Figure 2.3. These harmonic components are centered around  $m_f$  and its multiples,  $2m_f$  and  $3m_f$ . The harmonics makes additional losses such as copper and iron losses in motor, and they amplify torque ripple. The effectiveness of this waveform can be articulated by the total harmonic distortion (THD), as expressed in Equation 2.4, where  $v_k$  and  $i_k$  are the harmonic components of the voltage and current, and  $v_1$  and  $i_1$  are the fundamental component of the voltage and current. A lower THD value signifies that the waveform is closer to the sinusoidal form, leading to improved control performance and superior motor efficiency.

$$THD_{v} = \frac{\sqrt{\sum_{k=2}^{n} v_{k}^{2}}}{v_{1}}, \ THD_{i} = \frac{\sqrt{\sum_{k=2}^{n} i_{k}^{2}}}{v_{1}}$$

Equation 2.5

The linear modulation range is defined for when the MI is less than or equal to 1, while overmodulation is defined for when MI exceeds 1. The root mean square (rms) value of the fundamental line-to-line voltage  $V_{LL1}$  can be calculated using Equation 2.5 and Equation 2.6.

$$V_{LL1} = 0.612 \times m_a \cdot V_{DC}$$

, when  $m_a \le 1$  Equation 2.6

$$V_{LL1} = 0.78 \times V_{DC}$$

, when  $m_a > 1$  Equation 2.7

The maximum rms value of the line-to-line voltage are  $0.612V_{DC}$  and  $0.78V_{DC}$ , respectively. Despite its simplicity, SPWM has the disadvantage of being limited to a maximum output voltage of 0.612. Space Vector PWM (SVPWM) allows for more voltage utilization.

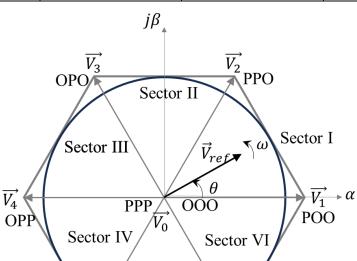

SVWPM is one of the widely used for EV traction inverter. In the context of switching states for a three-phase inverter, the "P" denotes that the top switch is in the onstate in the phase leg, whereas "O" signifies that the bottom switch is on. As displayed in Table 2.1, there are eight possible switching states in total. In the PPP state, referring to the circuit in Table 2.1, the upper switches (S1, S3, and S5) of the A, B, and C phases, respectively, are turn-on. Consequently, the space vector, the resultant of the vector sum of these three vectors, amounts to zero. Similarly, for the OOO state, where the bottom switches are on, the vector sum is also zero. These two scenarios are hence referred to as zero vectors. The other remained six states are the active vectors that are 60° out of phase with each other. These six active vectors form a hexagon in the space vector diagram, as seen in Figure 2.4. The hexagon that is generated from these six active vectors can be subdivided into a total of six sectors. Each sector corresponds to a unique combination of switch states, which in turn determines the output voltage vector of the inverter. The corresponding vector sums for each active states are presented in Table 2.1. These active vectors play a significant role in determining the inverter's output voltage and thus the performance and efficiency of the overall drive system.

Table 2.1. Space vector and on-state switch on 8 switching state of SVPWM.

| Space Vect  | tor                    | Switching State | <b>On-state Switch</b> | Vector Definition                      |

|-------------|------------------------|-----------------|------------------------|----------------------------------------|

| <b>a u</b>  | <b>&gt;</b>            | PPP             | S1, S3, S5             | 0                                      |

| Zero Vector | $\overrightarrow{V_0}$ | 000             | S2, S4, S6             | $\frac{2}{3}V_{DC}e^{j0}$              |

|             | $\overrightarrow{V_1}$ | POO             | S1, S4, S6             | $\frac{2}{3}V_{DC}e^{j\frac{\pi}{3}}$  |

|             | $\overrightarrow{V_2}$ | PPO             | S1, S3, S6             | $\frac{2}{3}V_{DC}e^{j\frac{\pi}{3}}$  |

| Active      | $\overrightarrow{V_3}$ | OPO             | S2, S3, S6             | $\frac{2}{3}V_{DC}e^{j\frac{2\pi}{3}}$ |

| Vector      | $\overrightarrow{V_4}$ | OPPP            | S2, S3, S5             | $\frac{2}{3}V_{DC}e^{j\frac{3\pi}{3}}$ |

|             | $\overrightarrow{V_5}$ | OOP             | S2, S4, S5             | $\frac{2}{3}V_{DC}e^{j\frac{4\pi}{3}}$ |

|             | $\overrightarrow{V_6}$ | РОР             | S1, S4, S5             | $\frac{2}{3}V_{DC}e^{j\frac{5\pi}{3}}$ |

Sector V

**Y**POP

$\overrightarrow{V_6}$

Figure 2.14. Space vector diagram of a two-level VSI

$OOP \xrightarrow{\checkmark} V_5$

The conception of this activation vector originates from Clarke's Transformation, which transforms the three-phase phase voltage, as demonstrated in Equation 2.7, into a stationary reference frame [20]. Clarke's Transformation, or  $\alpha$ - $\beta$  transformation, is a mathematical technique employed in the analysis and control of three-phase systems. This transformation simplifies the mathematical complexity involved in the analysis of three-phase systems, making it easier to visualize and control these systems.

$$\begin{bmatrix} \nu_{\alpha} \\ \nu_{\beta} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} \nu_{AO} \\ \nu_{BO} \\ \nu_{CO} \end{bmatrix}$$

Equation 2.8

$v_{\alpha}$  and  $v_{\beta}$  are the two-phase voltages in the  $\alpha$ - $\beta$  plane. From these, the space vector can be expressed as Equation 2.10 by combined Equation 2.7, 2.8, and 2.9. Each space vector obtained from these in shown in Table 2.1.

$$\vec{V} = v_{\alpha} + jv_{\beta}$$

Equation 2.9

$$e^{jx} = \cos x + j \sin x$$

Equation 2.10

$$\vec{V} = \frac{2}{3} \left[ v_{AO} e^{j0} + v_{BO} e^{j2\pi/3} + v_{CO} e^{j2\pi/3} \right]$$

Equation 2.11

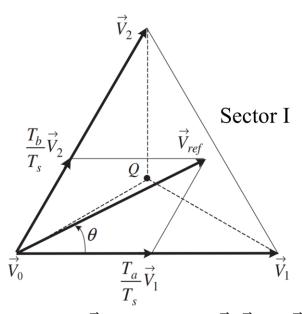

In Figure 2.4, the reference voltage  $\vec{V}_{ref}$  to be controlled rotates at a speed  $\omega$ . Essentially, what this implies is that a reference voltage, with a magnitude defined by the length of  $\vec{V}_{ref}$  and a specified speed  $\omega$ , can be synthesized by the suitable combination of active vectors available in this space vector diagram for each switching state. The dwell time for the stationary active vectors represents the duty-cycle of the chosen switches during a sampling period  $T_s$ .  $\vec{V}_{ref}$  can be synthesized as a combination of one zero vector and two adjacent vectors in the space vector plane. The dwell time of each vector can be accurately calculated using the relationship expressed in Equations 2.11 and 2.12, where  $T_a$ ,  $T_b$ , and  $T_0$  are the dwell time for the vector  $\vec{V}_1$ ,  $\vec{V}_2$ , and  $\vec{V}_0$ , respectively.

$$\vec{V}_{ref}T_s = \vec{V}_1T_a + \vec{V}_2T_b + \vec{V}_0T_0$$

Equation 2.12

$$T_s = T_a + T_b + T_0$$

Equation 2.13

The dwell time when  $\vec{V}_{ref}$  is at Sector I can be expressed by Equation 2.13, and shown in Figure 2.5.

$$T_{a} = \frac{\sqrt{3}T_{s}V_{ref}}{V_{DC}}\sin\left(\frac{\pi}{3} - \theta\right)$$

$$T_{b} = \frac{\sqrt{3}T_{s}V_{ref}}{V_{DC}}\sin(\theta)$$

Equation 2.14

$$T_{0} = T_{s} - T_{a} - T_{b}$$

Figure 2.15. The reference voltage  $\vec{V}_{ref}$  synthesized by  $\vec{V}_1$ ,  $\vec{V}_2$ , and  $\vec{V}_0$  when  $\vec{V}_{ref}$  is at Sector I.

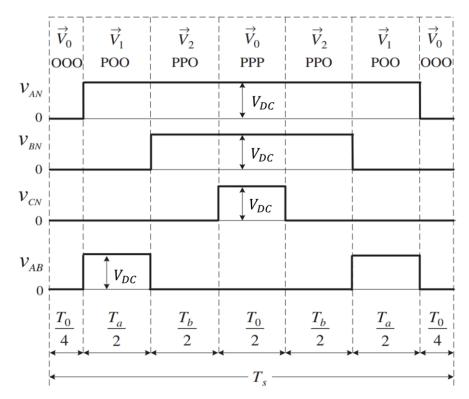

Figure 2.16. Typical seven-segment switching sequence for  $\vec{V}_{ref}$  in Sector I.

The switching sequence shall be designed to minimize the number of switching during sampling period. Figure 2.6 presents the typical switching sequence with seven-

segment in Sector I. Figure 2.6 illustrates the switching sequence for Sector 1, composed of a standard seven-segment pattern. By powering the three-phase switches on and off in this designated order, a reference voltage can be generated with the fewest possible number of switching operations. The order of switching for other sectors should also follow a sequence that leads to the minimum number of switching per period. This minimization of switching events contributes to a decrease in switching losses, thereby improving the overall efficiency of the system.

As depicted in Figure 2.4, the maximum controllable voltage using SVPWM is equal to the radius of the inscribed circle within the hexagon. At this maximum, the rms value of the line-to-line voltage is  $0.707V_{DC}$ . Hence, SVPWM, while being a more complex control scheme compared to others, enables a higher voltage utilization. This contributes to improved power quality and efficiency, justifying its implementation despite the complexity.

#### 2.1.2 Comparison of Multi-level Inverter Topology

As described in previous chapter, the most common type of inverter topology used in EVs is the two-level inverter. However, multi-level inverter topologies have gained increasing attention in recent years due to their potential benefits. Research has been conducted on various types of multi-level inverters due to their advantages such as high efficiency, high power density, better output waveform quality, low dv/dt and EMI, and inherent fault-tolerance [21-25]. This is particularly significant in high-voltage and highpower applications. Recently, high-voltage electric drive systems like 800V systems have gained attention, making multi-level inverter topologies a fresh alternative in this field. Compared to the traditional 400V system, the 800V system offers benefits such as faster battery charging speed, high efficiency due to lower motor current, which in turn reduces copper loss, and a decrease in cable thickness [26]. However, the high voltage can lead to a high dv/dt, impacting not only the power device of the inverter but also the insulation characteristics of the motor, potentially affecting reliability. A multi-level inverter can serve as an effective solution to this problem. The most common types of multi-level inverters are the diode-clamped, flying capacitor (FC), and cascaded H-bridge (CHB) inverters.

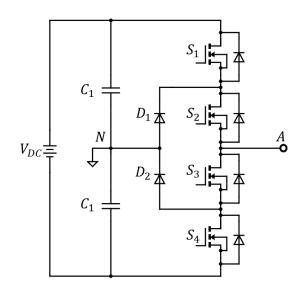

The diode-clamped inverter, also known as a neutral-point-clamped (NPC) inverter which was introduced by Nabae et al. [27], uses diodes to clamp the DC link voltage to achieve different voltage levels. This inverter was modelled to produce a small harmonic output voltage for a high efficiency motor drive. Figure 2.7 presented a three-level NPC topology. The additional neutral point of the converter allows the three states of the voltage level  $V_{DC}/2$ ,  $-V_{DC}/2$ , and 0. For  $V_{DC}/2$ , S1and S2 should be turned on, while S3 and S4 are turned on for  $-V_{DC}/2$ . And for 0 state, S2 and S3 should be turned on.

Figure 2.17. Three-level NPC inverter topology

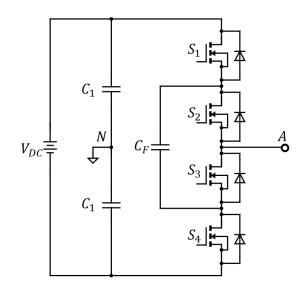

In comparison with other multilevel topologies, NPC inverter has been widely used due to high efficiency and simplicity [28-30]. This system utilizes a common DC-link, which offers the benefit of compactness by minimizing the number of capacitors required. However, if precise monitoring and control mechanisms are not in place, several drawbacks may arise. These include the risk of overcharging and discharging of the DC voltage, as well as uneven distribution of losses among the switches. To mitigate these issues, it is crucial to implement accurate monitoring and complex control techniques within the system [31]. The FC inverter uses capacitors instead of the clamping diodes to divide the DC link voltage into different levels [32]. The three-level FC inverter topology is presented in Figure 2.8. In the design of this topology, it's typical that one would need (n-1) capacitors for *n* distinct output voltage levels and  $(n-1) \times (n-2)/2$  flying capacitors are needed. These capacitors are arranged in a ladder-like configuration, with each subsequent capacitor possessing a different voltage than its neighboring capacitor. In the case of FC switching technology, the switching mechanism is comparable to that of a NPC inverter, with a slight variation in the 0 state [33]. For the 0 level, either S1, S3 or S2, S4 is turned on. A notable advantage of this topology is that it provides redundancies for inner voltage levels. This means that multiple valid switching combinations can produce the desired output voltage. Furthermore, the redundancy of clamped capacitors in each phase helps maintain balanced capacitor voltages, a feature that has been validated in numerous studies [34]-[36]. However, a major drawback to this topology lies in its requirement for a large number of capacitors. This requirement results in significant space implications, which negatively affect the power density of the inverter.

Figure 2.18. Three-level FC inverter topology.

Figure 2.9 shows the CHB inverter topology. This inverter consists of a series of H-bridge cells, each connected to a separate DC source, which provides different voltage levels [37]. When one H-bridge is connected, it has a three voltage levels. For producing